# **OEM Systems Handbook**

Order Number: 210941-003

### LITERATURE

In addition to the product line handbooks listed below, the INTEL PRODUCT GUIDE (no charge, Order No. 210846-003) provides an overview of Intel's complete product lines and customer services.

Consult the INTEL LITERATURE GUIDE (Order No. 210620) for a listing of Intel literature. TO ORDER literature in the U.S., write or call the INTEL LITERATURE DEPARTMENT, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only). TO ORDER literature from international locations, contact the nearest Intel sales office or distributor (see listings in the back of most any Intel literature).

Use the order blank on the facing page or call our TOLL FREE number listed above to order literature. Remember to add your local sales tax.

#### 1985 HANDBOOKS

Product line handbooks contain data sheets, application notes, article reprints and other design information.

|                                                                                                                                                 | *U.S. PRICE |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| QUALITY/RELIABILITY HANDBOOK (Order No. 210997-001) Contains technical details of both quality and reliability programs and principles.         | \$15.00     |

| CHMOS HANDBOOK (Order No. 290005-001) Contains data sheets only on all microprocessor, peripheral, microcontroller and memory CHMOS components. | \$12.00     |

| MEMORY COMPONENTS HANDBOOK (Order No. 210830-004)                                                                                               | \$18.00     |

| TELECOMMUNICATION PRODUCTS HANDBOOK (Order No. 230730-003)                                                                                      | \$12.00     |

| MICROCONTROLLER HANDBOOK (Order No. 210918-003)                                                                                                 | \$18.00     |

| MICROSYSTEM COMPONENTS HANDBOOK (Order No. 230843-002)<br>Microprocessors and peripherals—2 Volume Set                                          | \$25.00     |

| DEVELOPMENT SYSTEMS HANDBOOK (Order No. 210940-003)                                                                                             | \$15.00     |

| OEM SYSTEMS HANDBOOK (Order No. 210941-003)                                                                                                     | \$18.00     |

| SOFTWARE HANDBOOK (Order No. 230786-002)                                                                                                        | \$12.00     |

| MILITARY HANDBOOK (Order No. 210461-003)<br>Not available until June.                                                                           | \$15.00     |

| COMPLETE SET OF HANDBOOKS (Order No. 231003-002) Get a 25% discount off the retail price of \$160.                                              | \$120.00    |

### **U.S. LITERATURE ORDER FORM**

| NAME:                                                                                              | TITLE:                                                                                                                            |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| COMPANY:                                                                                           |                                                                                                                                   |

| ADDRESS:                                                                                           |                                                                                                                                   |

| CITY:                                                                                              | STATE: ZIP:                                                                                                                       |

| COUNTRY:                                                                                           |                                                                                                                                   |

| PHONE NO.: ()                                                                                      |                                                                                                                                   |

|                                                                                                    | TITLE QTY. PRICE TOTAL                                                                                                            |

| Allow 4-6 weeks for delivery Pay by Visa, MasterCard, Check or Mo                                  | Totaloney Order, payable to Intel Literature. Purchase Orders                                                                     |

| ☐ Visa Account No<br>☐ MasterCard                                                                  | Expiration<br>Date                                                                                                                |

| Signature:                                                                                         |                                                                                                                                   |

| Mail To: Intel Literature Distribution Mail Stop SC6-714 3065 Bowers Avenue Santa Clara. CA 95051. | Customers outside the U.S. and Canada should contact the local Intel Sales Office or Distributor listed in the back of this book. |

For information on quantity discounts, call the 800 number below:

TOLL-FREE NUMBER: (800) 548-4725

Prices good until 12/31/85.

Source HB

For a free subscription to the European edition of SOLUTIONS please mail this card to one of the regional offices listed below:

#### Intel Corporation (UK) Ltd

Piper's Way Swindon, SN3 1RJ Wiltshire, England

#### Intel Corporation S.A.R.L.

5 Place de la Balance Silic 223 94528 Rungis Cedex France

#### Intel Corporation Italia Spa

Milanofiori, Palazzo E 20094 Assago (Milano)

Italy

#### Intel Semiconductor GmbH

SeidIstrasse 27 D-8000 Munchen 2 West Germany

#### Intel Sweden AB

Box 20092 Archimedesvagen 5 S-16120 Bromma Sweden

### OEM SYSTEMS HANDBOOK

1985

About The Cover:

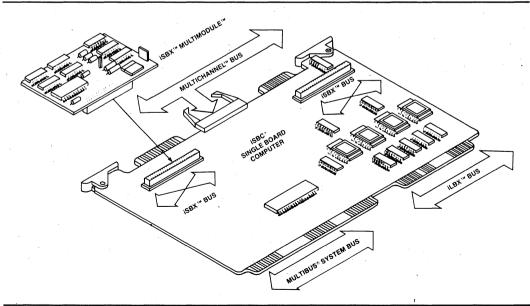

The cover design is an abstract portrayal of Intel's computer systems products as the building blocks of systems development. The building blocks meld together, encompassing the heart of an open system, which is symbolized by the pyramid at the heart of the architecture. This melding or flexibility is the key Intel provides to the design engineer for development of MULTIBUS® systems architecture.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, †, ICE, iCS, iDBP, iDIS, I²ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, int<sub>e</sub>lBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, OpeNET, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Ripplemode, RMX/80, RUPI, Seamless, SLD, SYSTEM 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

| CHAPTER 1                                             |             |

|-------------------------------------------------------|-------------|

| Integrated Microcomputer Systems                      |             |

| DATA SHEETS                                           |             |

| iXSM Series System Extention Modules                  | 1-1         |

| FACT SHEETS                                           |             |

| iDIS 715 Fact Sheet                                   | 1-3         |

| iRMX Language                                         | 1-8         |

| iRMX Operating System                                 | 1-13        |

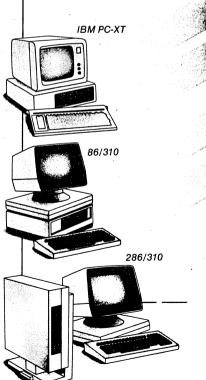

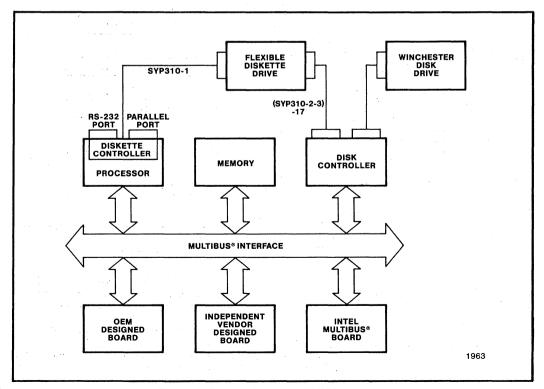

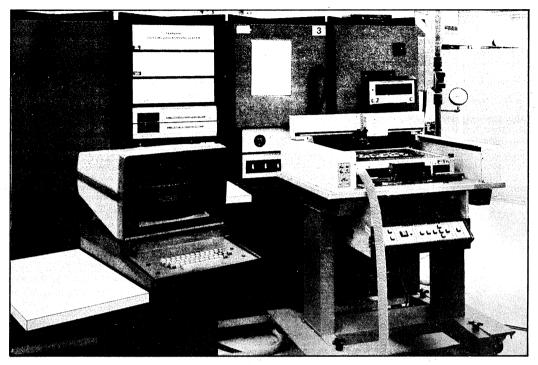

| System 310 Microcomputer System                       | 1-19        |

| System 380 Microcomputer Systems                      | 1-24        |

| Third Party Software For Intel Systems                | 1-30        |

| XENIX* Languages                                      | 1-33        |

| XENIX* 3.0 Operating System                           | 1-37        |

| 310 MS-DOS (2.11) Operating System Release 10         | 1-43        |

| 311 Peripheral Expansion Sub-system                   | 1-47        |

| RELIABILITY REPORTS                                   |             |

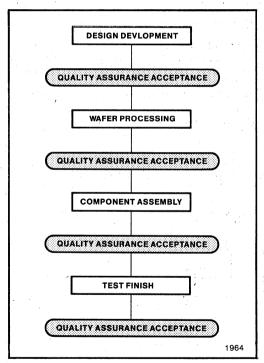

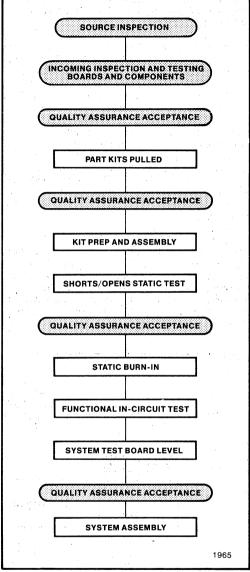

| System 310 Reliability                                | 1-51        |

| Gystom o to nonazmy                                   |             |

| CHAPTER 2                                             |             |

| Single Board Computers                                |             |

| DATA SHEETS                                           |             |

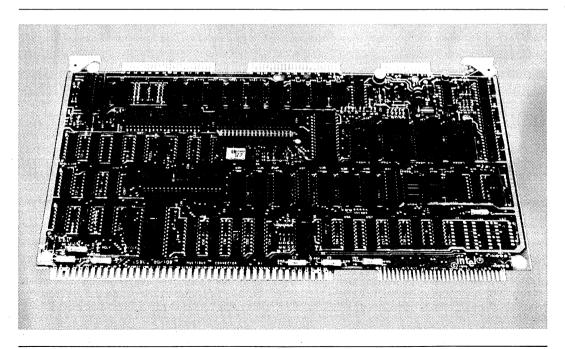

| iSBC 80/10B (or pSBC 80/10B*) Single Board Computer   | 2-1         |

| iSBC 80/20-4 (or pSBC 80/20-4*) Single Board Computer | 2-8         |

| iSBC 80/24 (or pSBC 80/24*) Single Board Computer     | 2-15        |

| iSBC 80/30 (or pSBC 80/30*) Single Board Computer     | 2-24        |

| iSBC 86/05 Single Board Computer                      | 2-32        |

| iSBC 86/12A (or pSBC 86/12A*) Single Board Computer   | 2-40        |

| iSBC 86/14 and iSBC 86/30 Single Board Computer       | 2-48        |

| iSBC 86/35 Single Board Computer                      | 2-56        |

| iSBC 88/25 Single Board Computer                      | 2-66        |

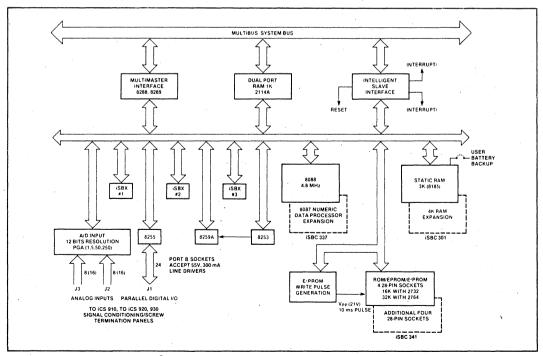

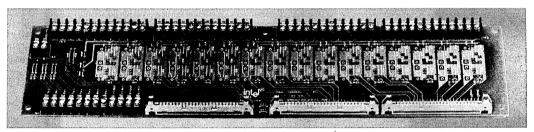

| iSBC 88/40 Measurement and Control Computer           | 2-74        |

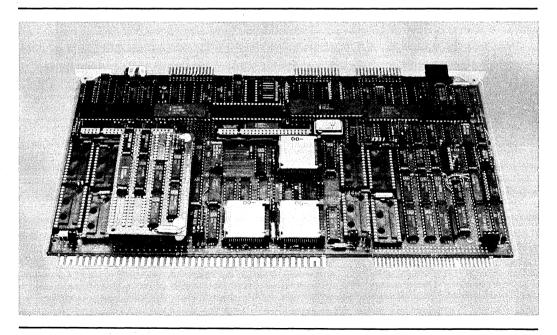

| iSBC 186/03 Single Board Computer                     | 2-82        |

| iSBC 286/10 Single Board Computer                     | 2-93        |

| APPLICATION NOTES                                     | 2 00        |

| AP-114 Using the iSBC 88/40                           |             |

| Measurement and Control Computer in PID Applications  | 2-102       |

| ARTICLE REPRINTS                                      |             |

| AR-229 Enhanced μC Boards                             |             |

| Strengthen Factory and Office Controllers             | 2-124       |

| AR-267 Choosing A Bus For Control                     |             |

| AR-268 Standard Buses Capture Fancy of Most OEM's     | 2-137       |

| ATT-200 Standard Edges Capture Failey of Most Cent 5  | 2 10        |

| CHAPTER 3                                             |             |

| MULTIBUS I Architecture                               |             |

| DATA SHEETS                                           |             |

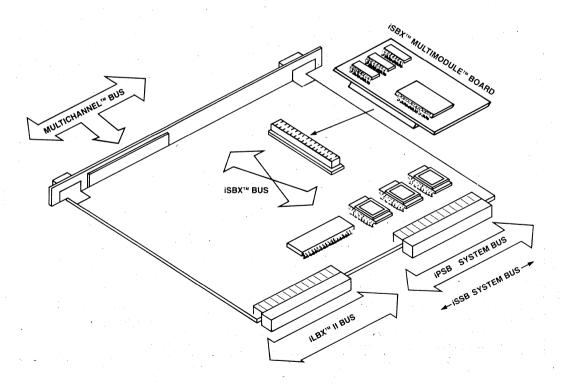

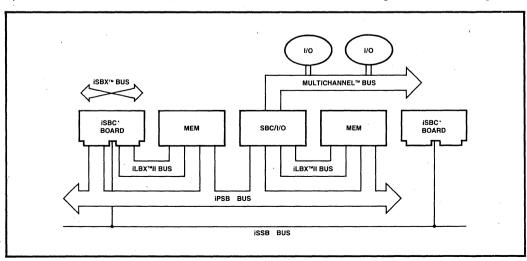

| MULTIBUS System Bus                                   | 3-1         |

| MULTICHANNEL I/O Bus                                  | 3-1<br>3-11 |

|                                                       | 3-11        |

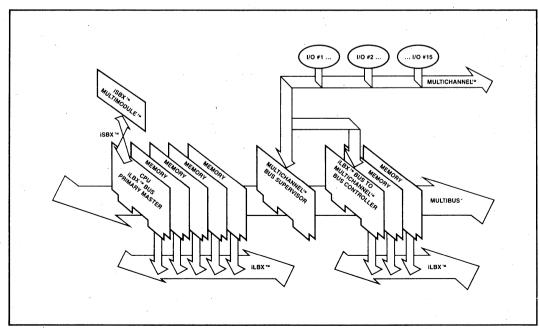

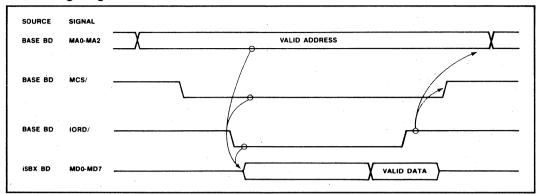

| iLBX Execution Bus                                    | 3-28        |

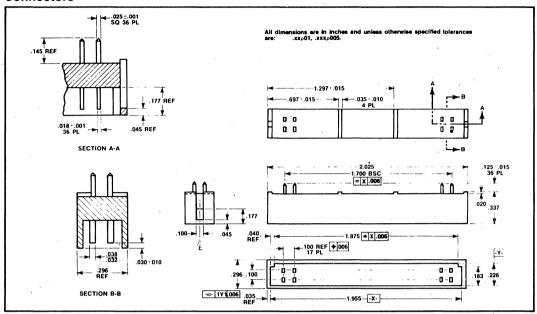

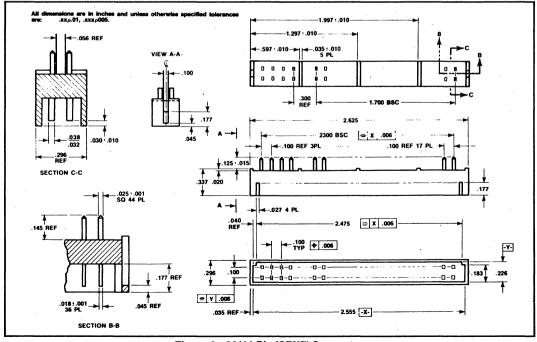

| iSBX I/O Expansion Bus                                | J-20        |

<sup>\*</sup>XENIX is a trademark of Microsoft Corporation

| CHAPTER 3 (continued)                                                                       |        |

|---------------------------------------------------------------------------------------------|--------|

| MULTIBUS I Architecture                                                                     |        |

| APPLICATION NOTES                                                                           |        |

| AP-28A Intel MULTIBUS Interfacing                                                           | 3-38   |

|                                                                                             |        |

| CHAPTER 4                                                                                   |        |

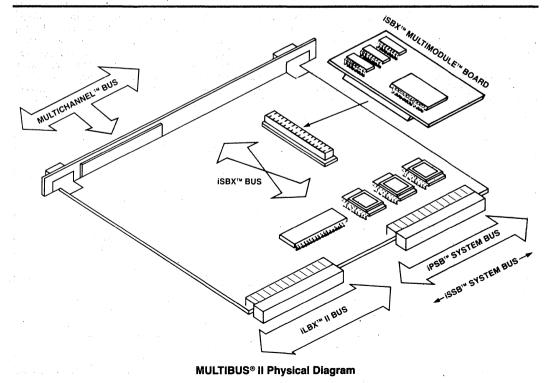

| MULTIBUS II Architecture and Products                                                       |        |

| DATA SHEETS                                                                                 |        |

| MULTIBUS II iLBX II Local Bus Extension                                                     | 4-1    |

| MULTIBUS II iPSB Parallel System Bus                                                        |        |

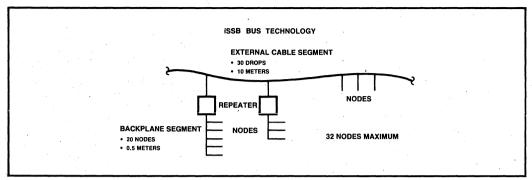

| MULTIBUS II iSSB Serial System Bus                                                          |        |

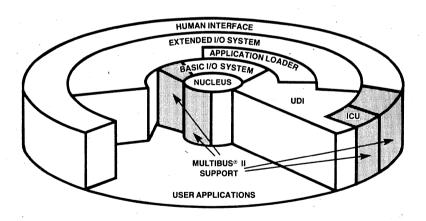

| iRMX 86 MULTIBUS II Support Package                                                         |        |

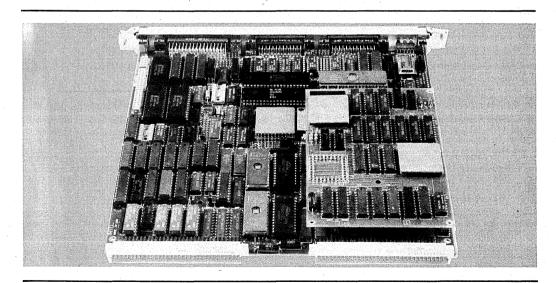

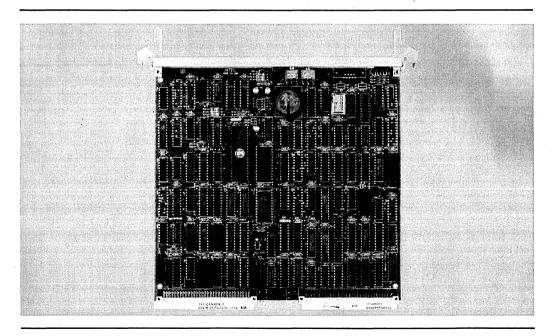

| iSBC 286/100 MULTIBUS II Single Board Computer                                              |        |

| iSBC MEM/312, 310, 320, 340 Cache-based MULTIBUS II Ram Boards                              |        |

| iSBC pkg 606/iSBC pkg 609 MULTIBUS II Cardcage Assemblies                                   |        |

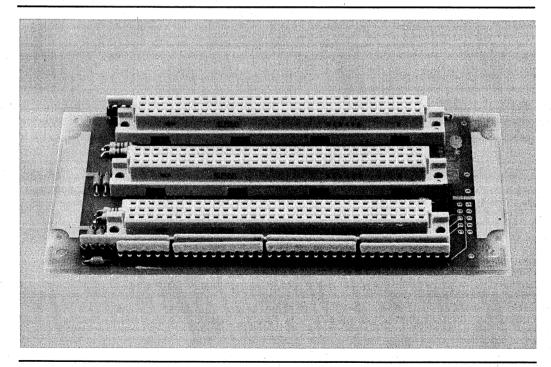

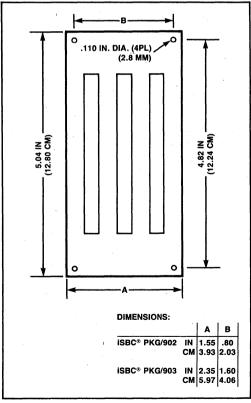

| iSBC pkg 902/iSBC pkg 903 MULTIBUS II iLBX II BackplaneiSBC CSM/001 Central Services Module |        |

| iSDM 286 iAPX 286 System Debug Monitor                                                      |        |

| ARTICLE REPRINTS                                                                            | 4-30   |

| AR-356 Multiprocessor Bus Is Ready To Meet 32-Bit Application                               |        |

| of The Future                                                                               | 4-54   |

| AR-350 Message Passing Supports Multiple Processor Design                                   |        |

|                                                                                             |        |

| CHAPTER 5                                                                                   |        |

| High Speed Math Boards                                                                      |        |

| DATA SHEETS                                                                                 |        |

| iSBX 331 Fixed/Floating Point Math MULTIMODULE Board                                        | 5-1    |

| iSBX 337/337A MULTIMODULE Numeric Data Processor                                            |        |

|                                                                                             | •      |

| CHAPTER 6                                                                                   |        |

| System Software                                                                             |        |

| DATA SHEETS                                                                                 |        |

| iOSP 86, iAPX 86/30, iAPX 88/30, iAPX 186/30 and                                            |        |

| iAPX 188/30 Support Package                                                                 | 6-1    |

| iRMX 86 Operating System                                                                    |        |

| iRMX 286 Operating System                                                                   |        |

| iRMX 51 Real-Time Multitasking Executive                                                    |        |

| iRMX 510 iDCM Support Package                                                               | 6-33   |

| iSDM 86 System Debug Monitor                                                                | 6-37   |

| OUADTED 7                                                                                   |        |

| CHAPTER 7                                                                                   |        |

| Memory Expansion Boards                                                                     | rsi tu |

| DATA SHEETS                                                                                 |        |

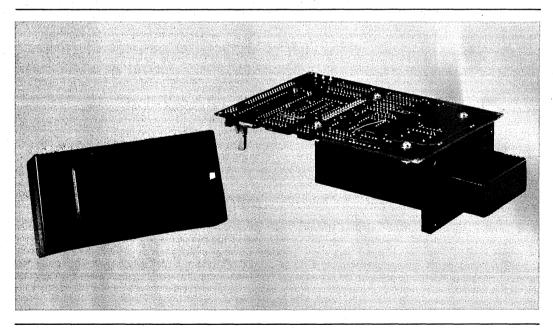

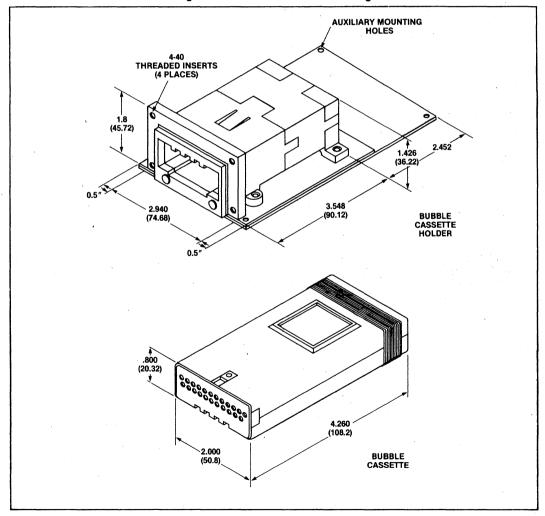

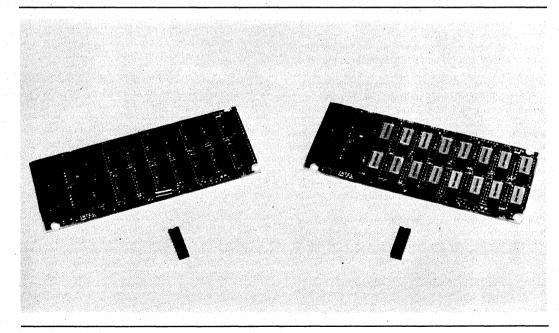

| iBCK 10-1 and iBCK 10-4 Intel Bubble Cassette System                                        |        |

| Production Kit                                                                              |        |

| iBCK 12 Intel Bubble Cassette Prototype Kit                                                 |        |

| iSBC 012B Ram Memory Boards                                                                 | 7-7    |

| iSBC 028C, 056C and 012C ECC Ram Boards                                                     |        |

| iSBC 028CX, 056CX, 012CX, 010CX and 020CX iLBX Ram Boards                                   |        |

| iSBC 028A/056A Ram Memory Boards                                                            | 7-18   |

| CHAPTER 7 (continued)                                            |       |

|------------------------------------------------------------------|-------|

| Memory Expansion Boards                                          |       |

| DATA SHEETS                                                      |       |

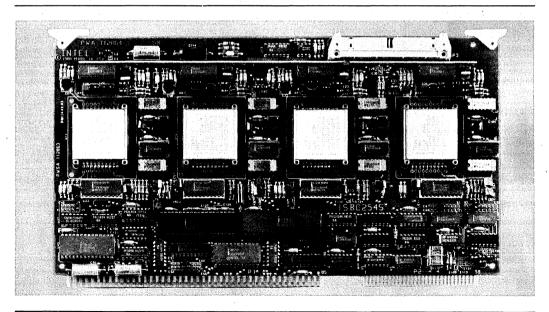

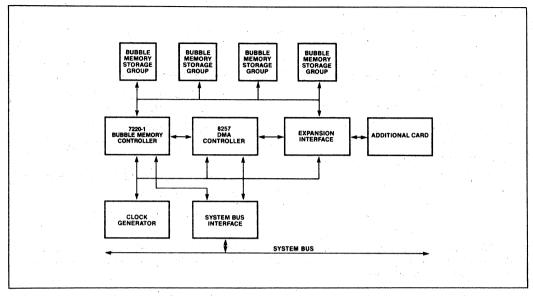

| iSBC 254S Bubble Memory Board                                    | 7-21  |

| iSBC 300 (or pSBC 300*) 32K Byte Ram Expansion Module            | 7-27  |

| iSBC 300A 32K Byte Ram MULTIMODULE Board                         | 7-24  |

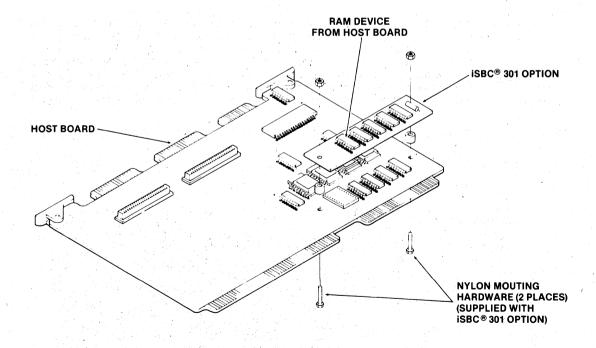

| iSBC 301 4K Byte MULTIMODULE Board                               | 7-31  |

| iSBC 302 8K Byte MULTIMODULE Ram                                 | 7-34  |

| iSBC 304 128K Byte Ram MULTIMODULE Board                         | 7-24  |

| iSBC 304C 128K Byte ECC MULTIMODULE Board                        | 7-36  |

| iSBC 307 128K Byte Ram MULTIMODULE Board With Parity             | 7-40  |

| iSBC 314 512K Byte Ram MULTIMODULE Board                         | 7-43  |

| iSBC 340 or (pSBC 340*) 16K Byte Expansion Module                | 7-27  |

| iSBC 341 28-Pin MULTIMODULE EPROM                                | 7-47  |

| iSBC 428 Universal Site Memory Expansion Board                   | 7-49  |

| iSBC 464 641K Byte EPROM Expansion Board                         | 7-53  |

| iSBX 251 and 251C Bubble Memory MULTIMODULE Board                | 7-56  |

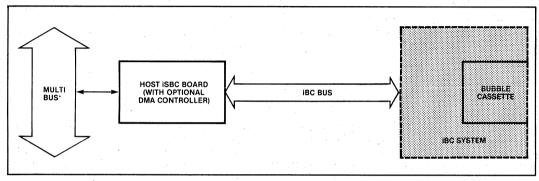

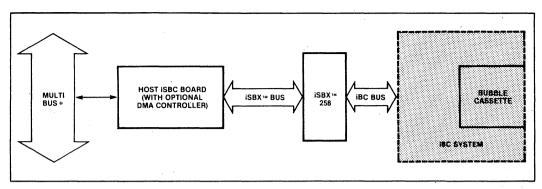

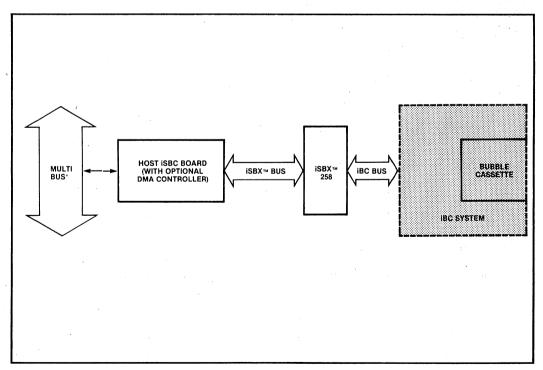

| iSBX 258 Interface MULTIMODULE For Intel Bubble Cassette System  | 7-61  |

| iSBC 340 (or pSBC 340) 16K Byte EPROM Expansion Module           | 7-27  |

|                                                                  |       |

| CHAPTER 8                                                        |       |

| Peripheral Controllers                                           |       |

| DATA SHEETS                                                      |       |

| iSBC 204 Single Density Flexible Diskette Controller             | 8-1   |

| iSBC 208 Flexible Diskette Controller                            | 8-4   |

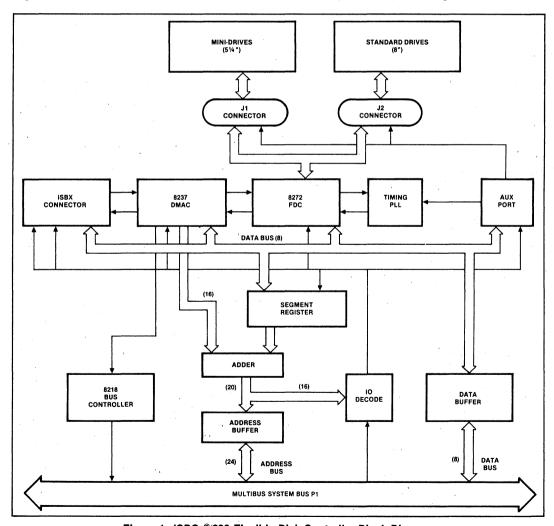

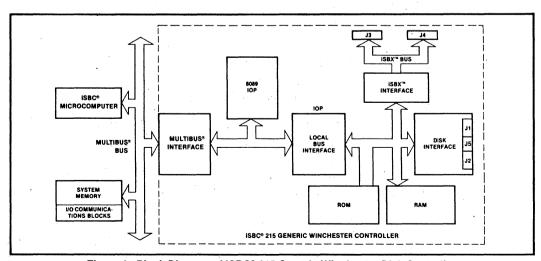

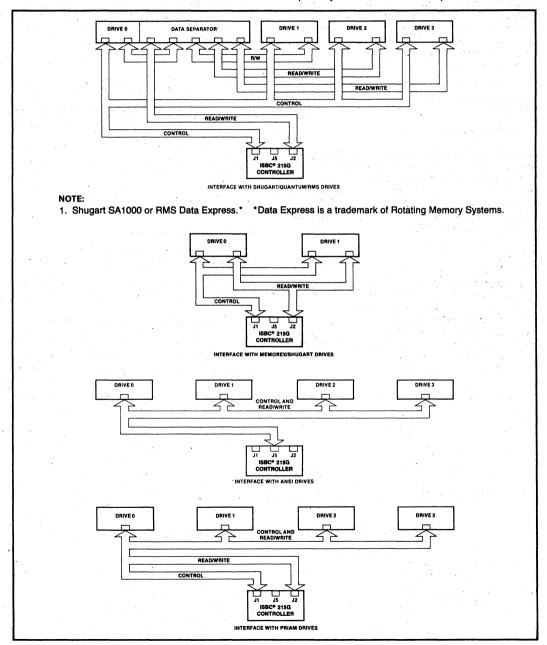

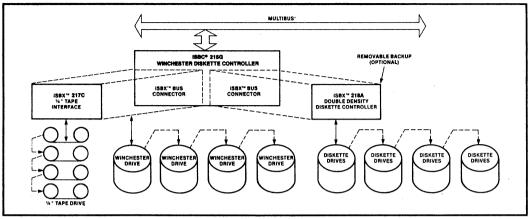

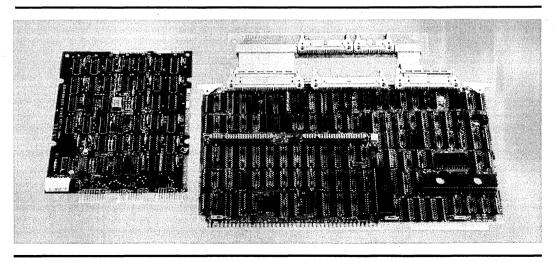

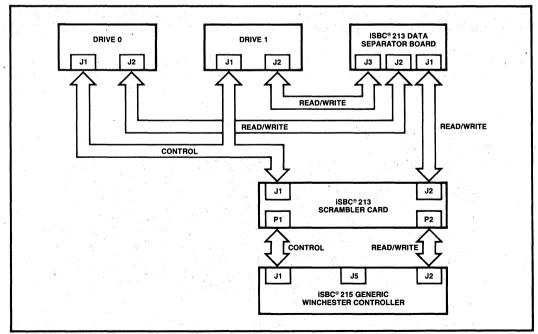

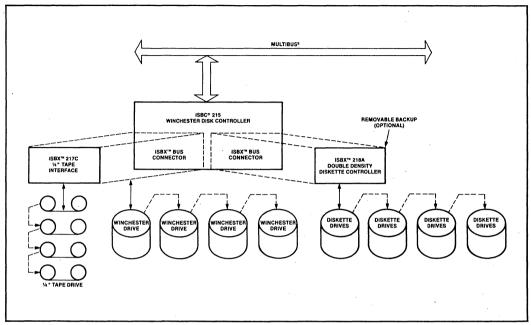

| iSBC 215 Generic Winchester Controller                           | 8-8   |

| iSBC 215G 5.25" Winchester Controller Kit                        | 8-13  |

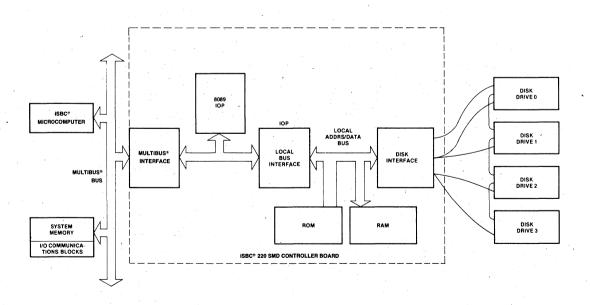

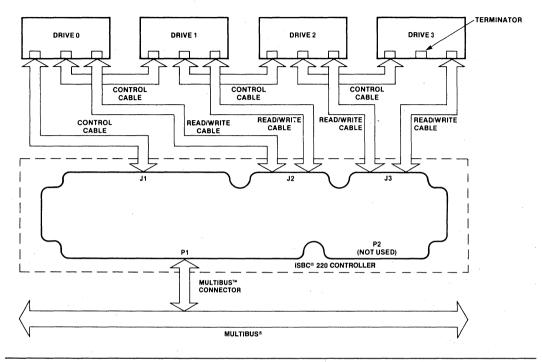

| iSBC 220 SMD Disk Controller                                     | 8-17  |

| iSBX 217C 1/4-inch Tape Drive Interface MULTIMODULE Board        | 8-21  |

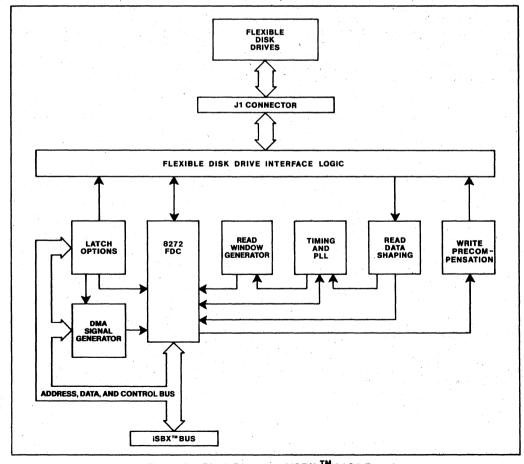

| iSBX 218A Flexible Disk Controller                               | 8-25  |

|                                                                  |       |

| CHAPTER 9                                                        |       |

| Human Interface                                                  |       |

| DATA SHEETS                                                      |       |

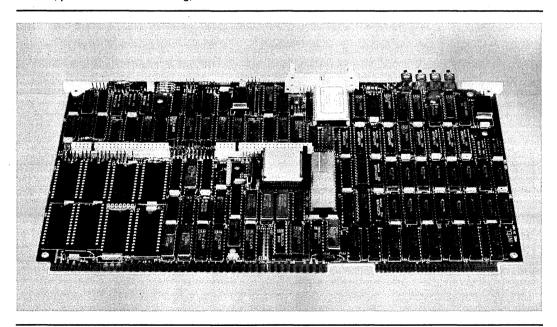

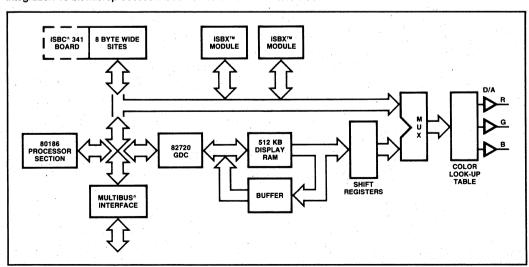

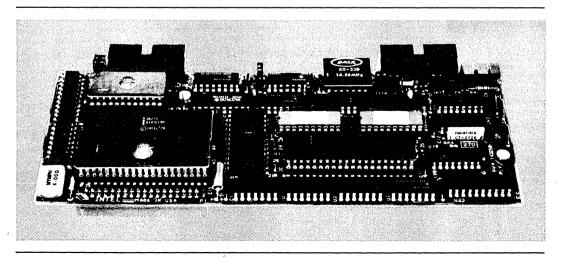

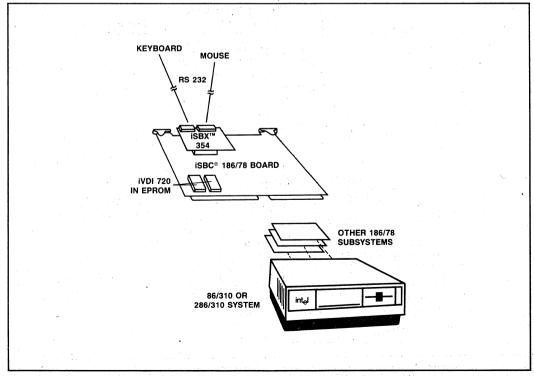

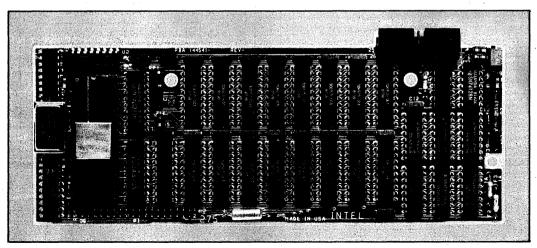

| iSBC 186/78 Intelligent Video Graphics Subsystem                 | 9-1   |

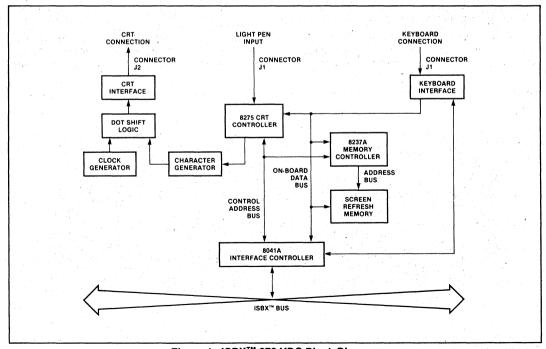

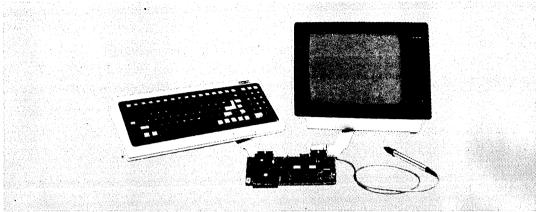

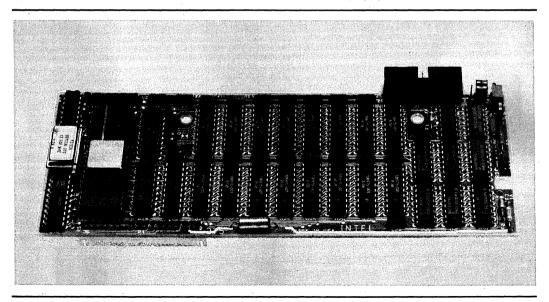

| iSBX 270 Alpha-Numeric Display Controller                        |       |

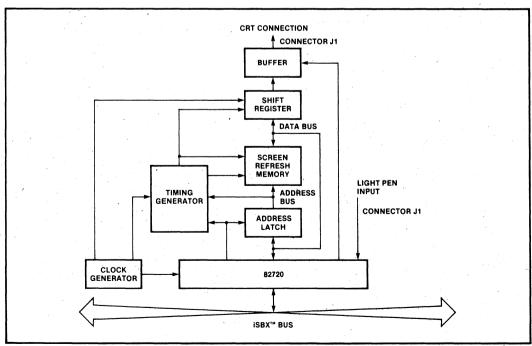

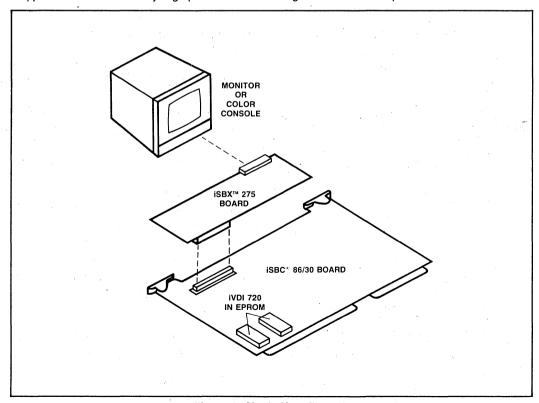

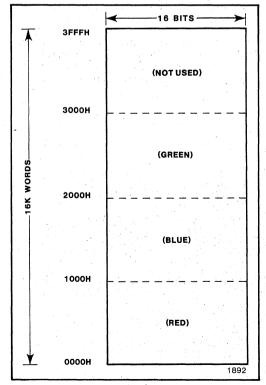

| iSBX 275 Video Graphics Controller                               | 9-11  |

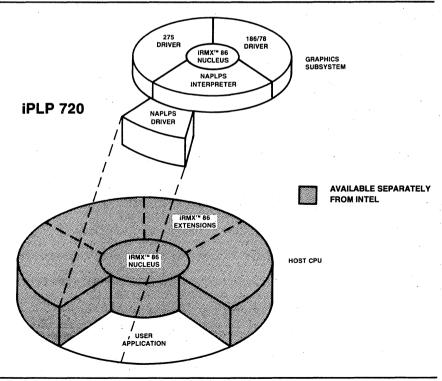

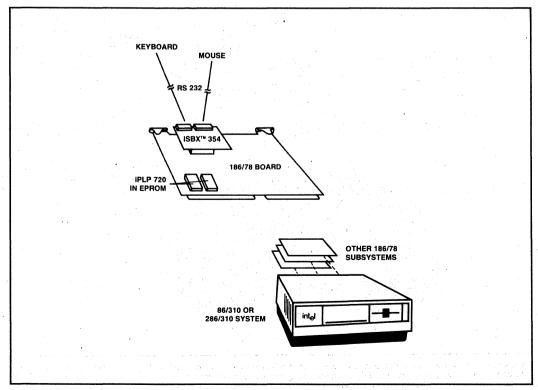

| iPLP 720 NAPLPS Interpreter                                      | 9-15  |

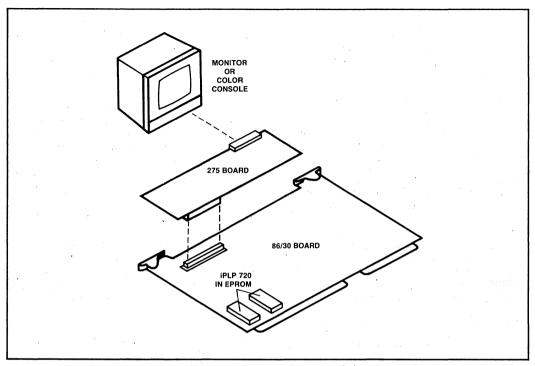

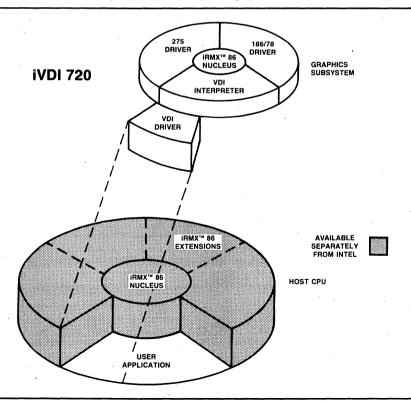

| iVDI 720 Graphics Virtual Device Interpreter                     | 9-19  |

| APPLICATION NOTES                                                |       |

| AP-180 Graphics Applications of The iSBX 275 Graphics Controller | 9-23  |

| ARTICLE REPRINTS                                                 |       |

| AR-284 Computer Graphics Needs Standards As a Foundation         |       |

| For Future Growth                                                | 9-79  |

|                                                                  |       |

| CHAPTER 10                                                       |       |

| Communications Controllers                                       |       |

| DATA SHEETS                                                      |       |

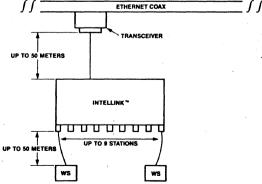

| iDCM 911-1 INTELLINK™ ETHERNET™ Cluster Module                   | 10-1  |

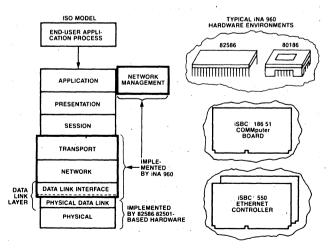

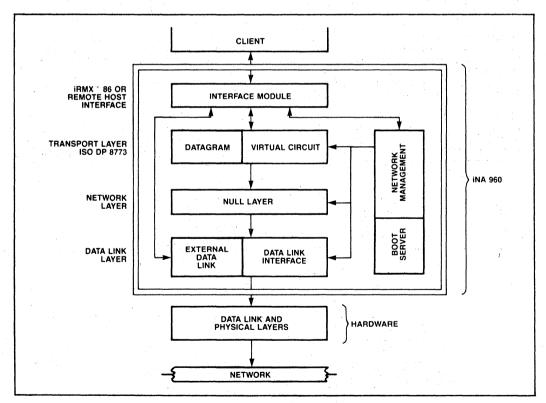

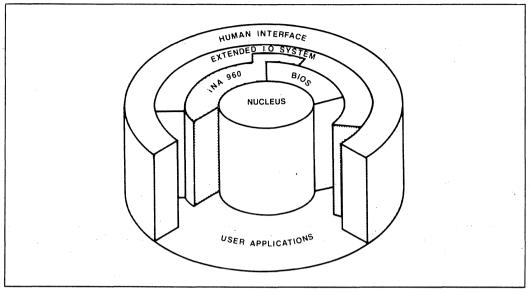

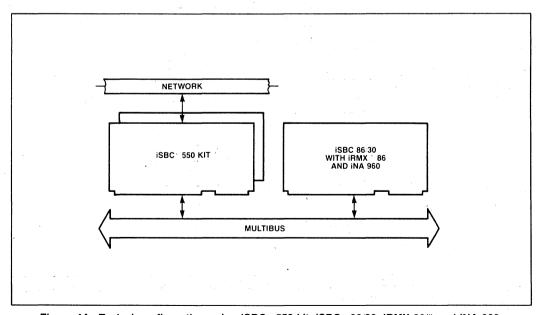

| iNA 960 Network Software                                         | 10-3  |

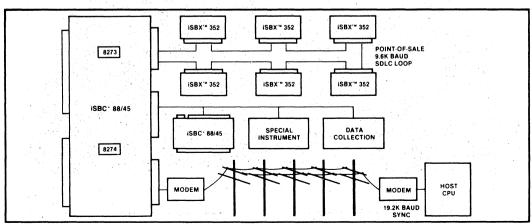

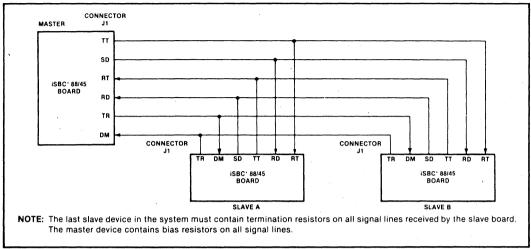

| iSBC 88/45 Advanced Data Communications Processor Board          | 10-15 |

| CHAPTER 10 (continued)                                                                                         |       |

|----------------------------------------------------------------------------------------------------------------|-------|

| Communications Controllers                                                                                     |       |

| DATA SHEETS                                                                                                    |       |

| iSBC 188/48 Advanced Communications Computer                                                                   | 10-24 |

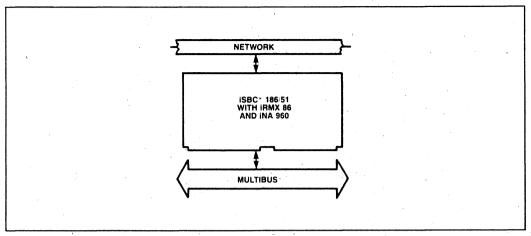

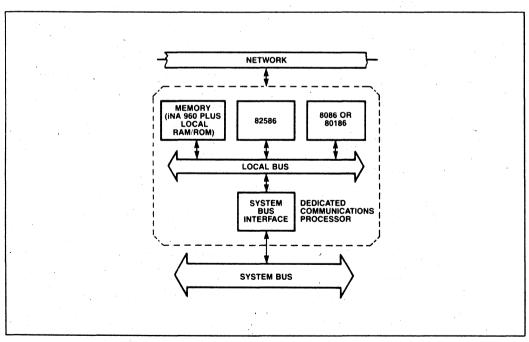

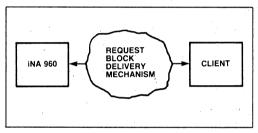

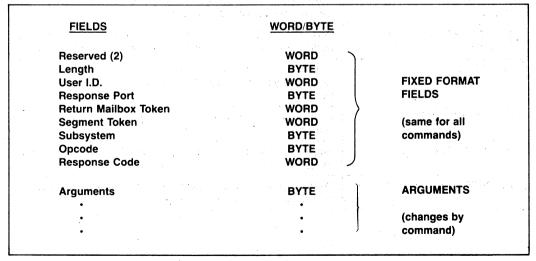

| iSBC 186/51 Communicating Computer                                                                             | 10-31 |

| iSBC 534 (or pSBC 534*) Four Channel Communication Expansion Board                                             | 10-50 |

| iSBC 544 Intelligent Communications Controller                                                                 | 10-54 |

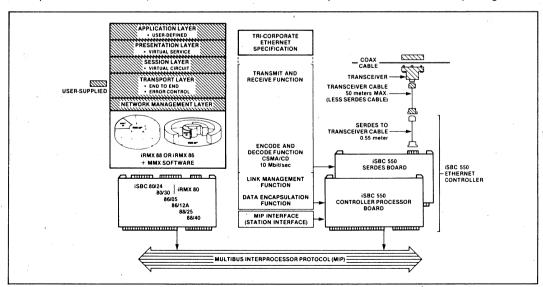

| iSBC 550 Ethernet Communications Controller                                                                    | 10-61 |

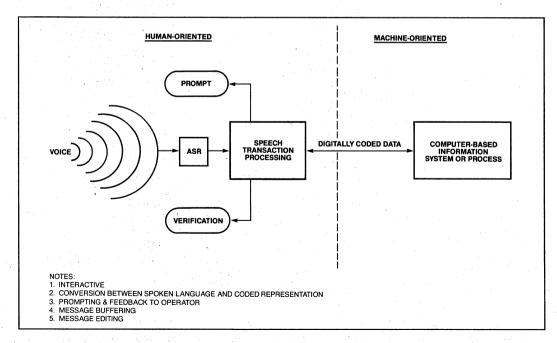

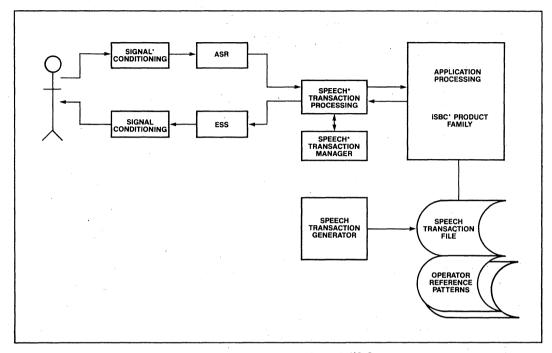

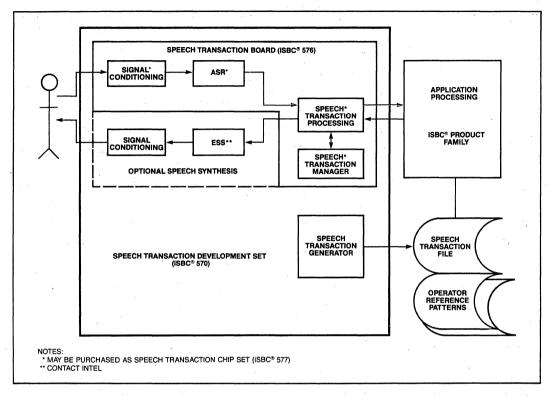

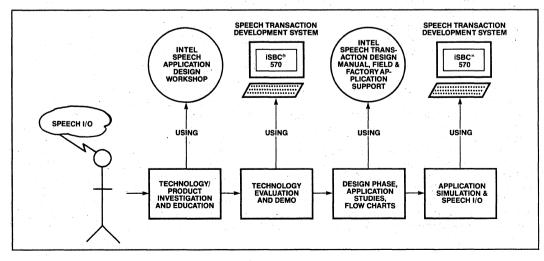

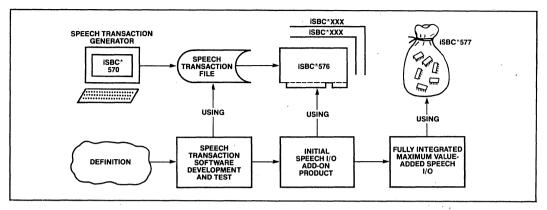

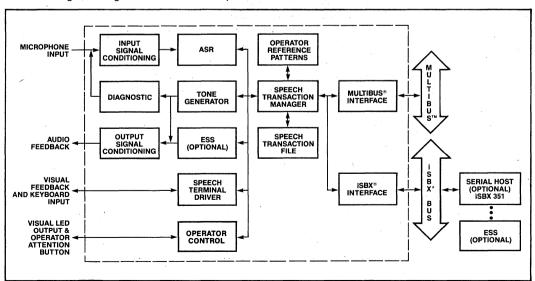

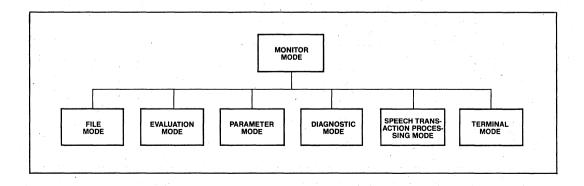

| iSBC 570, 576, 577 Intel Speech Transaction Family                                                             | 10-65 |

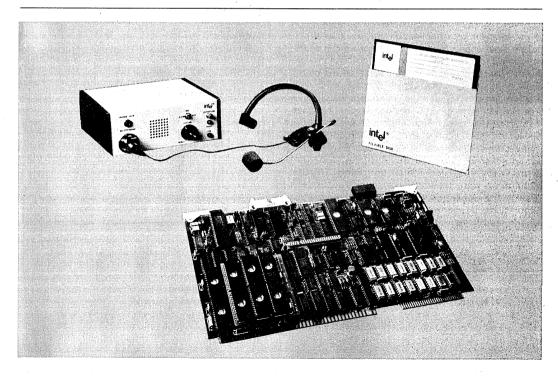

| iSBC 570 Speech Transaction Development Set                                                                    | 10-71 |

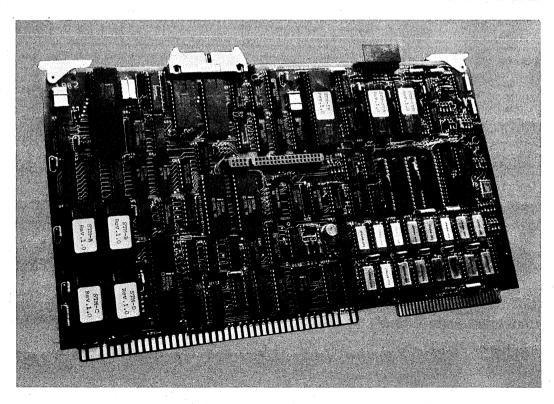

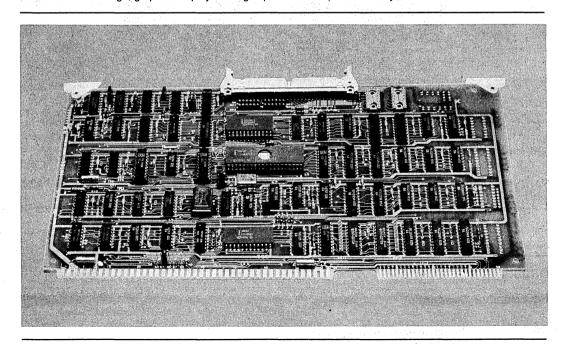

| iSBC 576 Speech Transaction Board                                                                              | 10-74 |

| iSBC 577 Speech Transaction Recognition Chip Set                                                               | 10-79 |

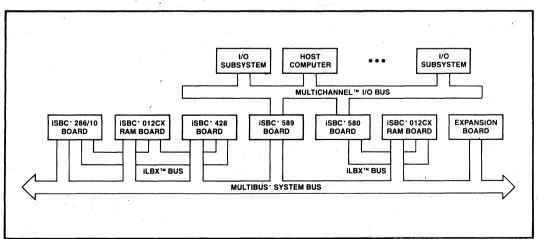

| iSBC 580 MULTICHANNEL Bus to iLBX Bus Interface                                                                | 10-80 |

| iSBC 589 Intelligent DMA Controller                                                                            | 10-84 |

| ka tagada a katalan da katalan katalan katalan da katalan da katalan da katalan da katalan da katalan da katal |       |

| CHAPTER 11 (1) (1) (1) (1) (1) (1) (1) (1) (2) (1) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2                      |       |

| Digital I/O Expansion and Signal Conditioning Boards                                                           |       |

| DATA SHEETS                                                                                                    |       |

| iSBC 517 Combination I/O Expansion Boards                                                                      | 11-1  |

| iSBC 519 (or pSBC 519") Programmable I/O Expansion Boards                                                      | 11-5  |

| iSBC 556 Optically Isolated I/O Board                                                                          | 11-9  |

|                                                                                                                | 11-11 |

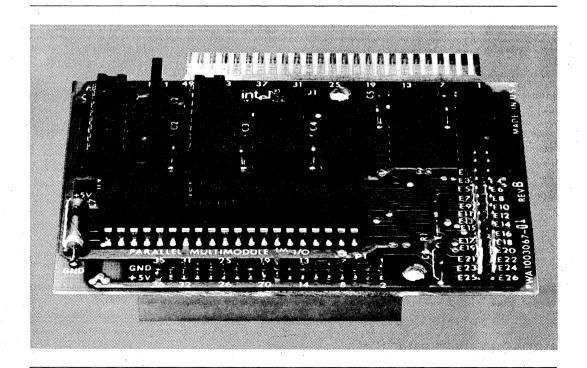

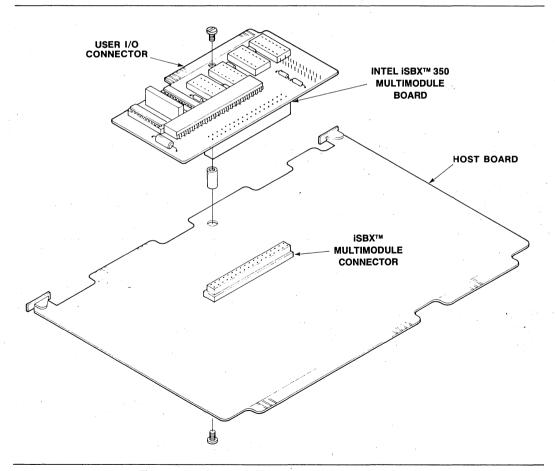

| iSBX 350 Parallel I/O MULTIMODULE Board                                                                        | 11-16 |

| iSBX 351 Serial I/O MULTIMODULE Board                                                                          | 11-20 |

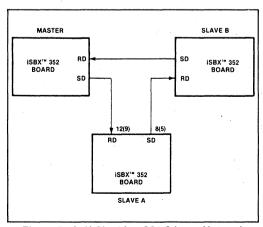

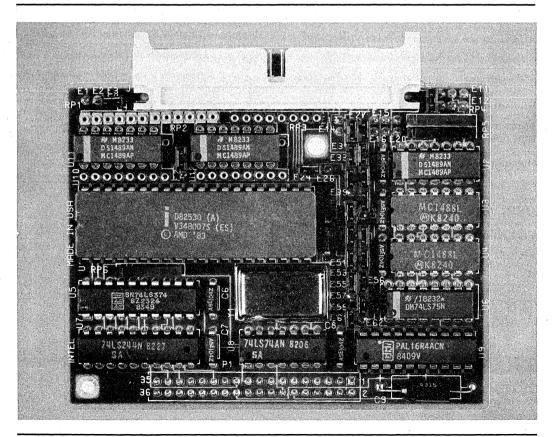

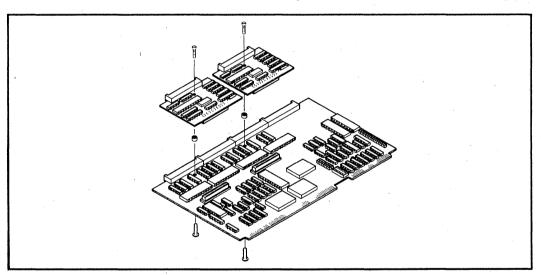

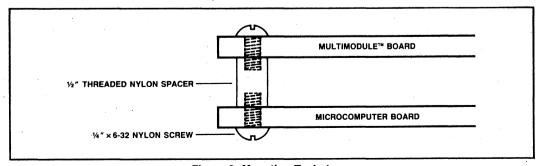

| iSBX 352 Bit Serial Communications MULTIMODULE Board                                                           | 11-26 |

| iSBX 354 Dual Channel Serial I/O MULTIMODULE Board                                                             | 11-32 |

| iSBX 488 GPIB MULTIMODULE Board                                                                                | 11-37 |

| APPLICATION NOTES                                                                                              |       |

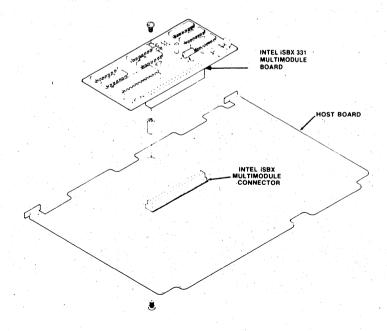

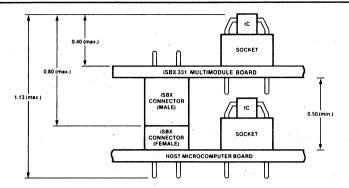

| AP-96 Designing iSBX MULTIMODULE Boards                                                                        | 11-41 |

|                                                                                                                |       |

| CHAPTER 12                                                                                                     |       |

| System Packaging and Power Supplies                                                                            |       |

| DATA SHEETS                                                                                                    | 4.1   |

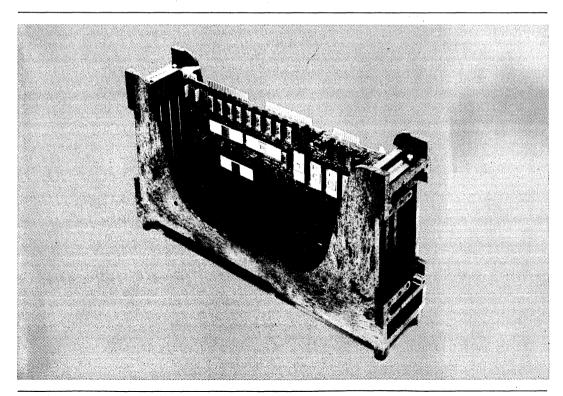

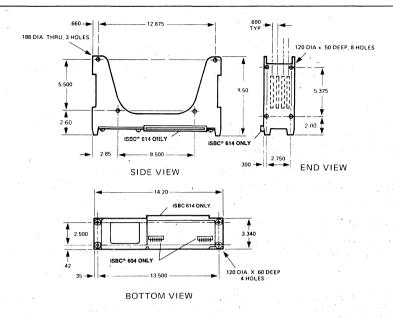

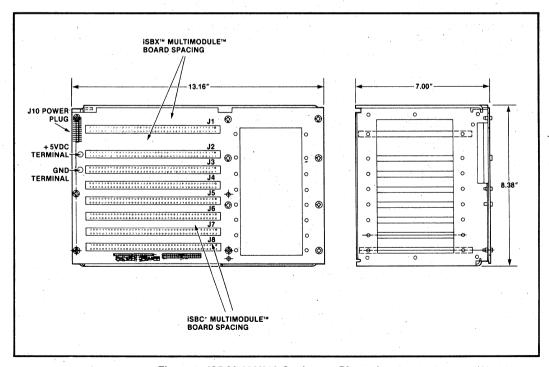

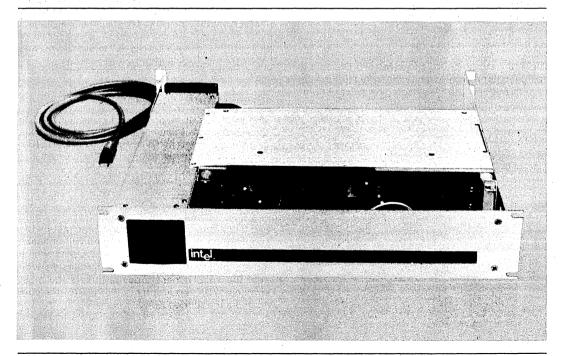

| iSBC 604/614 (or pSBC 604/614*) Modular Cardcage Assemblies                                                    |       |

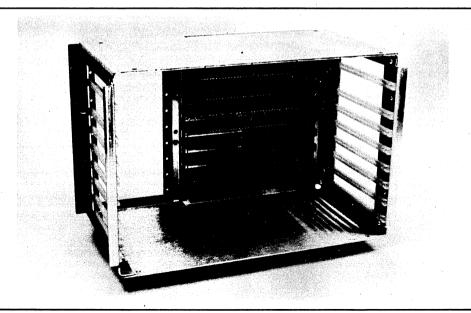

| iSBC 608/618 Cardcages                                                                                         | 12-3  |

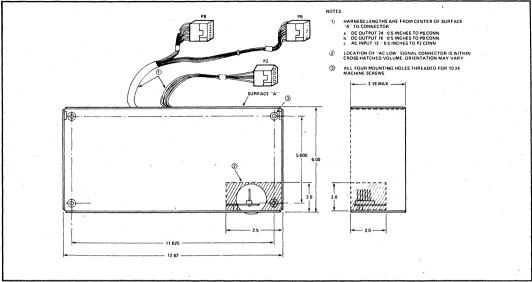

| iSBC 635 Power Supply                                                                                          | 12-7  |

| iSBC 640 Power Supply                                                                                          | 12-10 |

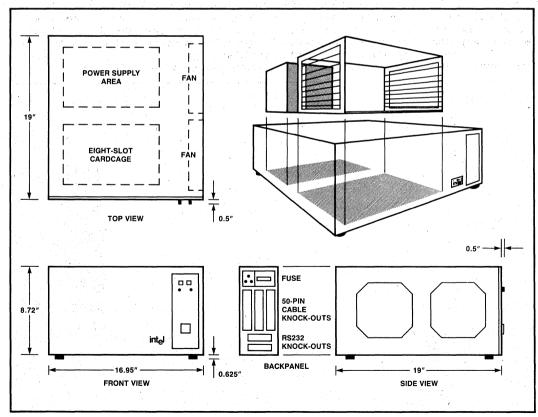

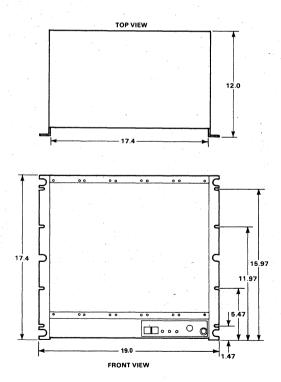

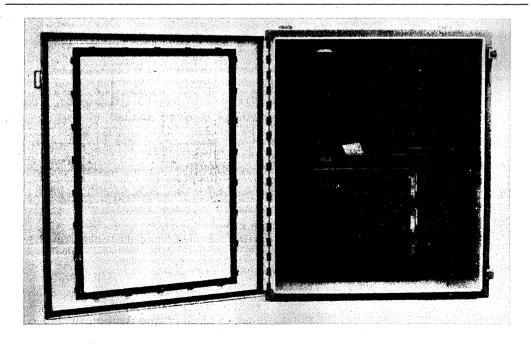

| iSBC 655 System Chassis                                                                                        | 12-12 |

| iSBC 660 System Chassis                                                                                        | 12-14 |

| iSBC 661 System Chassis                                                                                        | 12-17 |

| iSBC 665 System Chassis                                                                                        | 12-21 |

| iSYP 384 System Chassis                                                                                        | 12-25 |

|                                                                                                                |       |

| CHAPTER 13                                                                                                     |       |

| ICS Industrial Control Series and Analog I/O Expansion                                                         |       |

| DATA SHEETS                                                                                                    | 40    |

| iCS Industrial Chassis Kit 635, Kit 640                                                                        | 13-1  |

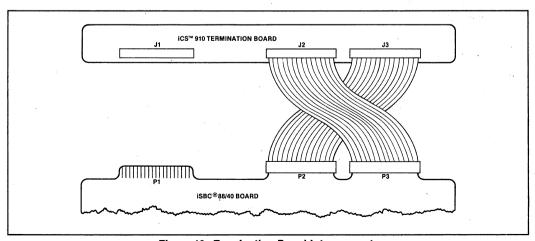

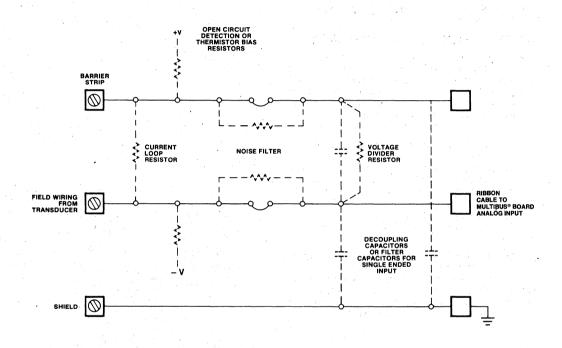

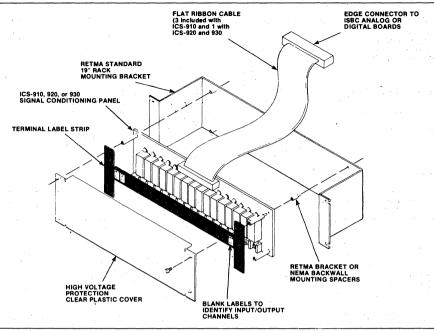

| iCS 910/920/930 Signal Conditioning/Termination Panels                                                         | 13-6  |

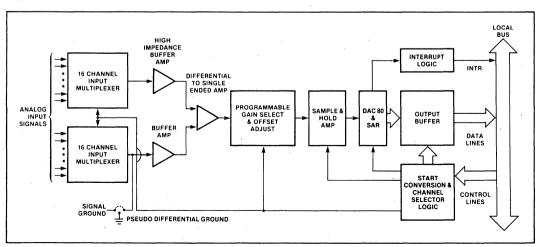

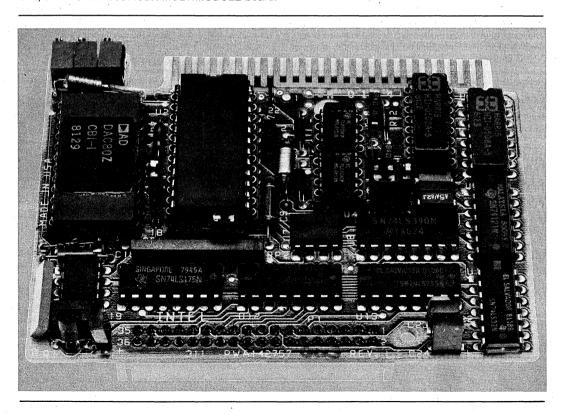

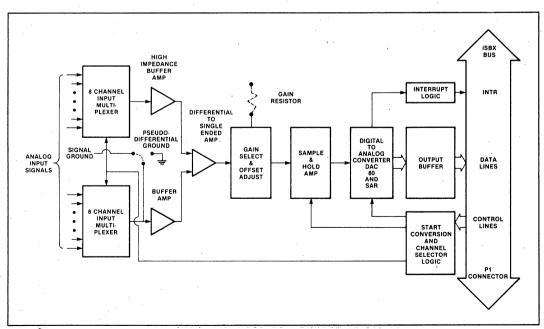

| iSBX 311 Analog Input MULTIMODULE Board                                                                        | 13-14 |

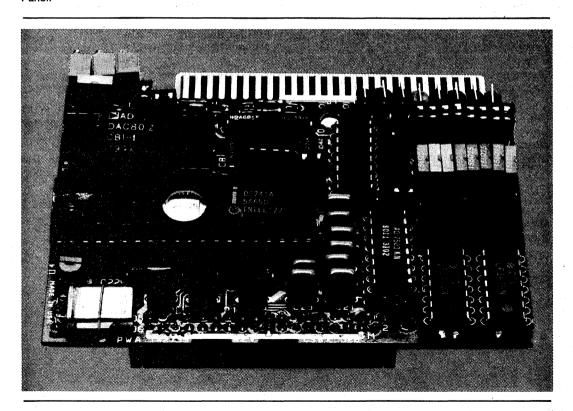

| iSBX 328 Analog Output MULTIMODULE Expansion Board                                                             | 13-18 |

| CHAPTER 13 (continued) ICS Industrial Control Series and Analog I/O Expansion APPLICATION NOTES | 40.00 |

|-------------------------------------------------------------------------------------------------|-------|

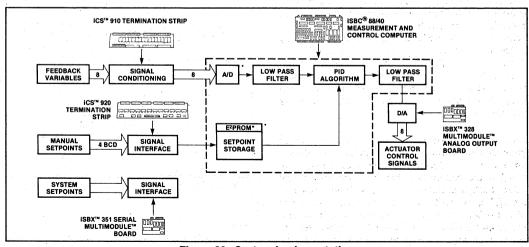

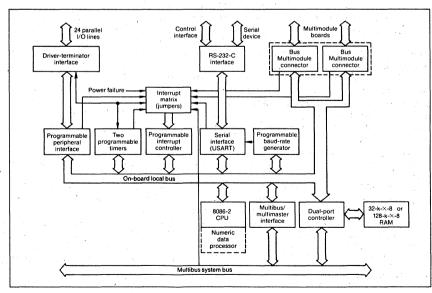

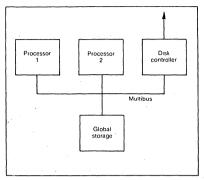

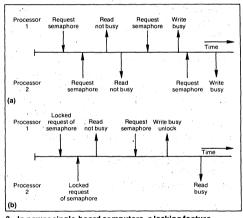

| AP-52 Using Intel's Industrial Control Series in Control                                        | 13-22 |

| CHAPTER 14                                                                                      |       |

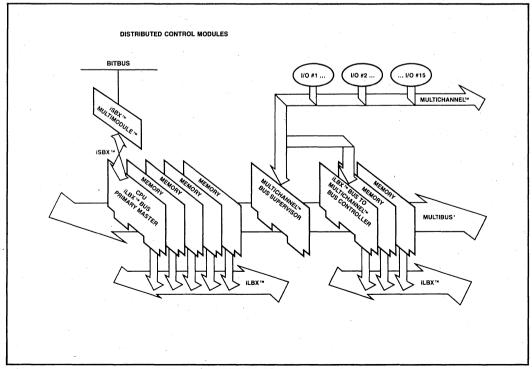

| Distributed Control Modules                                                                     |       |

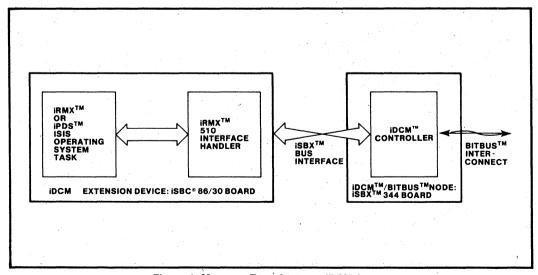

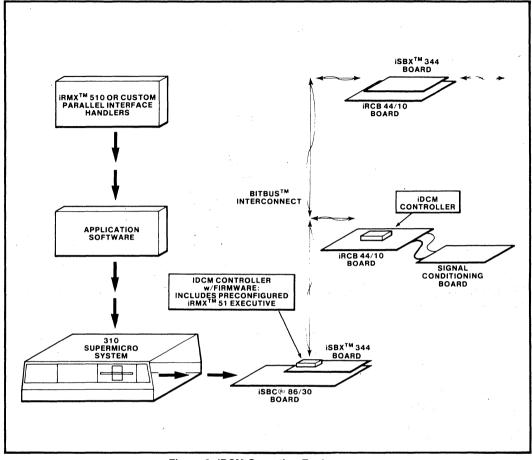

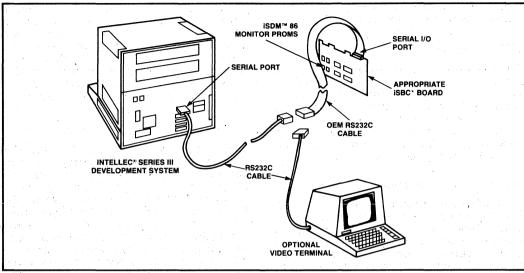

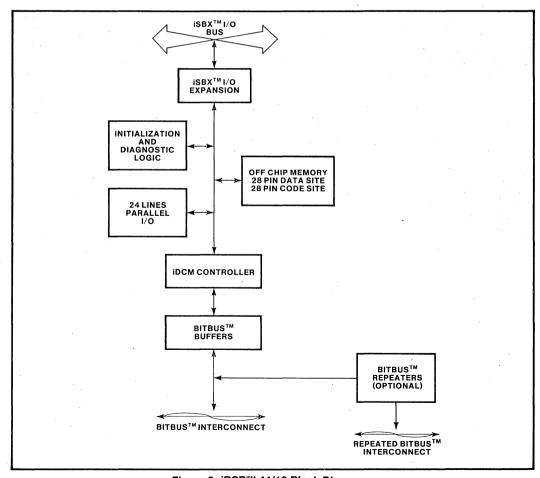

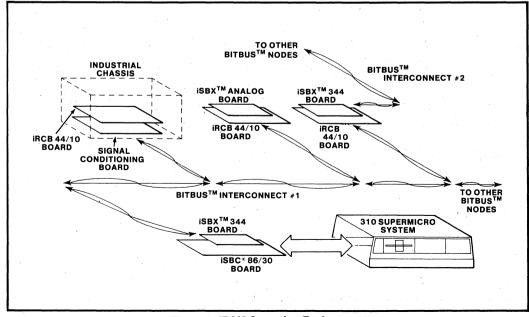

| iDCM Introduction                                                                               | 14-1  |

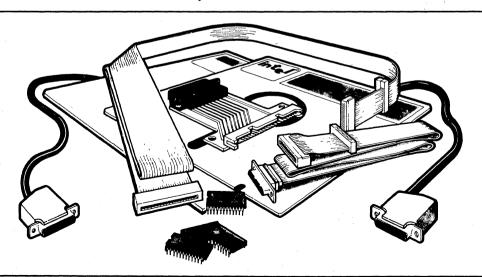

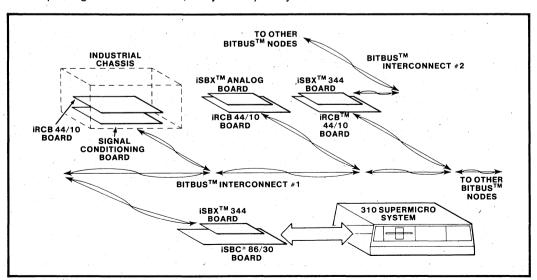

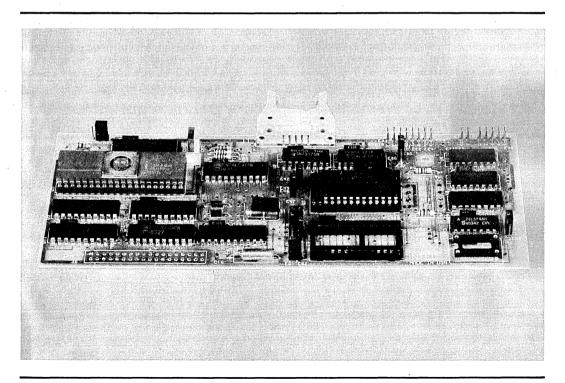

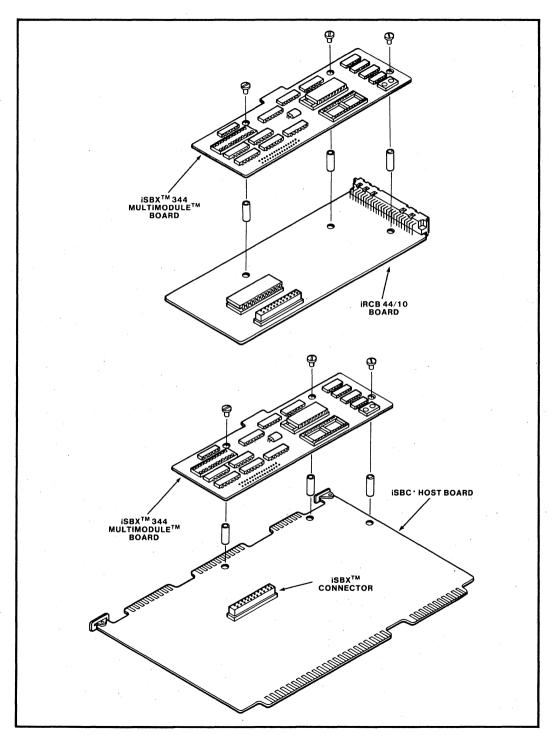

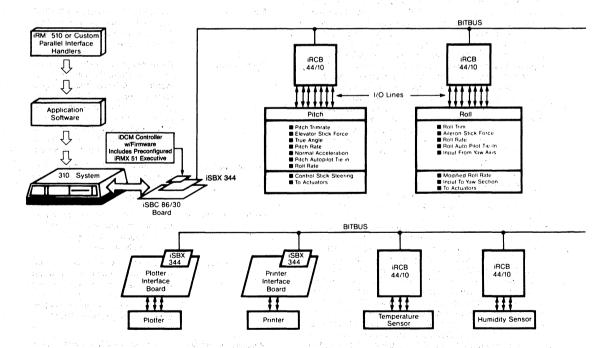

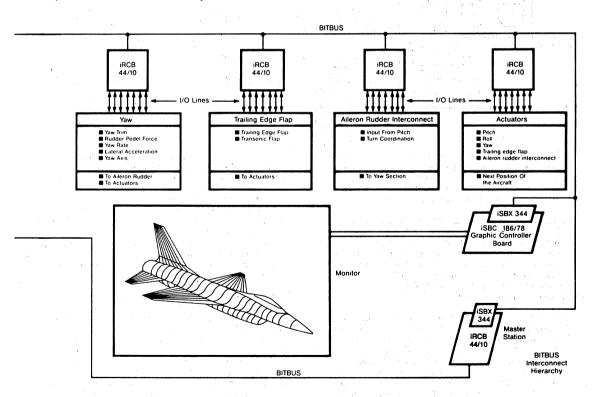

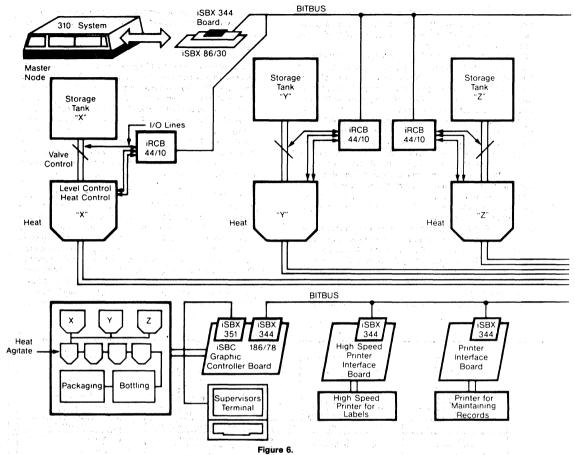

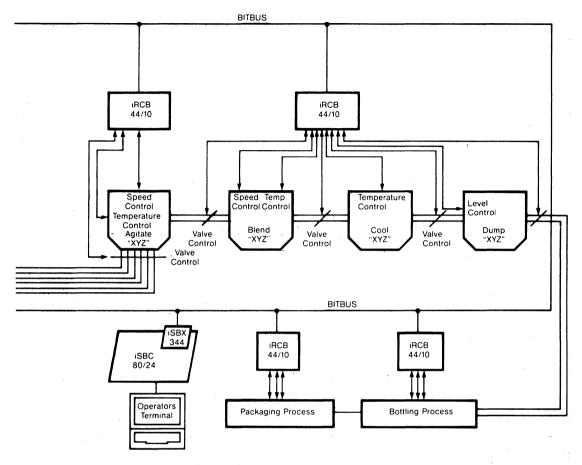

| IRCB 44/10 BITBUS Remote Controller Board                                                       | 14-5  |

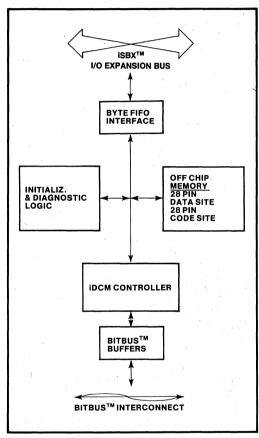

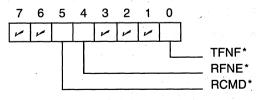

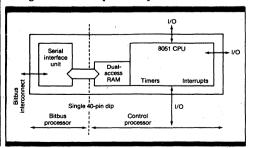

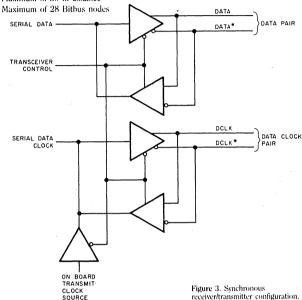

| iSBX 344 BITBUS Controller MULTIMODULE Board                                                    | 14-15 |

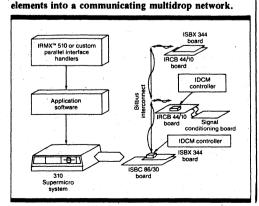

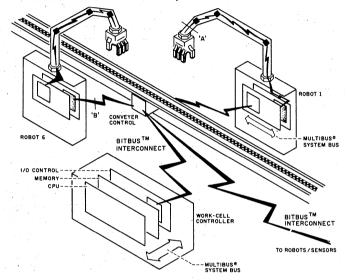

| AP-224 BITBUS Interconnect: From Flight Simulation To Process Control                           | 14-24 |

| AR-347 BITBUS Promises To Standardize Control                                                   | 14-32 |

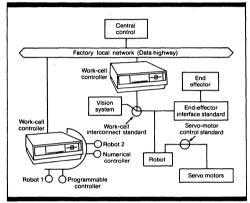

| Method of Robot Communication                                                                   | 14-38 |

| CHAPTER 15                                                                                      |       |

| Miscellaneous Services                                                                          |       |

| iMBX 100/110/120/130 MULTIBUS Exchange Hardware                                                 |       |

| Subscription Service                                                                            |       |

| iNSITE User's Program Library                                                                   |       |

| iRUG Description                                                                                | 15-7  |

# Alphanumeric Index

| iBCK 10-1 and iBCK 10-4 Intel Bubble Cassette System                         | 7-1   |

|------------------------------------------------------------------------------|-------|

| iBCK 12 Intel Bubble Cassette Prototype Kit                                  |       |

| iCS Industrial Chassis Kit 635, Kit 640                                      |       |

| iCS 910/920/930 Signal Conditioning Termination Panels                       |       |

| iDCM 911-1 INTELLINK™ ETHERNET™ Cluster Module                               |       |

| iDIS 715                                                                     |       |

| iLBX Execution Bus                                                           |       |

| iNA 960 Network Software                                                     | 10-3  |

| iOSP 86, iAPX 86/30, iAPX 88/30, iAPX 186/03 and iAPX 188/30 Support Package |       |

| iPLP 72 NAPLPS Interpreter                                                   | 9-15  |

| iRCB 44/10 BITBUS Remote Controlled Board                                    | 14-5  |

| iRUG Description                                                             |       |

| iRMX Language                                                                |       |

| iRMX Operating System                                                        | 1-13  |

| iRMX 51 Real-Time Multitasking Executive                                     |       |

| iRMX 86 MULTIBUS II Support Package                                          |       |

| iRMX 86 Operating System                                                     |       |

|                                                                              |       |

| iRMX 286 Operating System                                                    |       |

| iRMX 510 iDCM Support PackageiSBC CSM/001 Central Services Module            |       |

|                                                                              |       |

| iSBC MEM/312, 310, 320, 340 Cache-based MULTIBUS II Ram Boards               |       |

| iSBC pkg 606/609 MULTIBUS II Cardcage Assemblies                             |       |

| iSBC pkg 902/iSBC pkg 903 MULTIBUS II iLBX Backplane                         |       |

| iSBC 010CX iLBX Ram Boards                                                   |       |

| iSBC 012B Ram Memory Board                                                   |       |

| iSBC 012C ECC Ram Board                                                      |       |

| iSBC 012CX iLBX Ram Boards                                                   |       |

| iSBC 020CX iLBX Ram Board                                                    |       |

| iSBC 028C ECC Ram Board                                                      |       |

| iSBC 028CX iLBX Ram Board                                                    |       |

| iSBC 028A/056A Ram Memory Boards                                             |       |

| ISBC 056C ECC Ram Board                                                      |       |

| iSBC 80/10B (or pSBC 80/10B*) Single Board Computer                          |       |

| iSBC 80/20-4 (or pSBC 80/20-4*) Single Board Computer                        |       |

| iSBC 80/24 (or pSBC 80/24*) Single Board Computer                            |       |

| iSBC 80/30 (or pSBC 80/30*) Single Board Computer                            |       |

| iSBC 86/05 Single Board Computer                                             | 2-32  |

| iSBC 86/12A (or pSBC 86/12A*) Single Board Computer                          |       |

| iSBC 86/14 Single Board Computer                                             |       |

| iSBC 86/30 Single Board Computer                                             |       |

| iSBC 86/35 Single Board Computer                                             |       |

| iSBC 88/25 Single Board Computer                                             | 2-66  |

| iSBC 88/40 Measurement and Control Computer                                  |       |

| iSBC 88/45 Advanced Data Communications Processor Board (3-Channel)          | 10-15 |

| iSBC 186/03 Single Board Computer                                            |       |

| iSBC 186/51 Communicating Computer                                           | 10-24 |

| iSBC 186/78A Intelligent Graphics Subsystem                                  |       |

| iSBC 188/48 Advanced Communications Computer (8-Channel)                     | 10-31 |

| iSBC 204 Single Density Flexible Diskette Controller                         |       |

| iSBC 208 Flexible Diskette Controller                                        | . 8-4 |

# Alphanumeric Index

| iSBC 215 Generic Winchester Controller                             | 8-8   |

|--------------------------------------------------------------------|-------|

| iSBC 215 5.25" Winchester Controller                               |       |

| iSBC 220 SMD Disk Controller                                       |       |

| iSBC 254S Bubble Memory Boards                                     |       |

| iSBC 286/10 Single Board Computer                                  |       |

| iSBC 286/100 MULTIBUS Single Board Computer                        |       |

| iSBC 300 (or pSBC 300*) 32K Byte Ram Expansion Module              |       |

| iSBC 300A 32K Byte Ram MULTIMODULE board                           |       |

| iSBC 301 4K Byte MULTIMODULE Board                                 |       |

| iSBC 302 8K Byte MULTIMODULE Ram                                   |       |

| iSBC 304 128K Byte Ram MULTIMODULE Board                           |       |

| iSBC 304C 128K Byte ECC MULTIMODULE Board                          |       |

| iSBC 307 128K Byte Ram MULTIMODULE Board With Parity               |       |

| iSBC 314 512K Byte Ram MULTIMODULE Board                           |       |

| iSBC 340 (or pSBC 340) 16K Byte EPROM Expansion Module             |       |

| iSBC 341 28-Pin MULTIMODULE ERPOM                                  |       |

| iSBC 428 Universal Site Memory Expansion board                     |       |

| iSBC 464 641K Byte EPROM Expansion Board                           |       |

| iSBC 517 Combination I/O Expansion Boards                          |       |

| iSBC 519 (or pSBC 519*) Programmable I/O Expansion Boards          |       |

| iSBC 534 (or pSBC 534*) Four Channel Communication Expansion Board | 10-50 |

| iSBC 544 Intelligent Communication Controller (4-Channel)          |       |

| iSBC 550 Ethernet Communications Controller                        |       |

| iSBC 556 Optically Isolated I/O Board                              |       |

| iSBC 569 Intelligent Digital Controller                            |       |

| iSBC 570 Speech Transaction Development Set                        |       |

| iSBC 576 Speech Transaction Board                                  |       |

| iSBC 577 Speech Transaction Recognition Chip Set                   |       |

| iSBC 580 MULTICHANNEL Bus To iLBX Bus Interface                    |       |

| iSBC 589 Intelligent DMA Controller                                |       |

| iSBC 604/614 (or pSBC 604/614*) Modular Cardcage Assemblies        |       |

| iSBC 608/618 Cardcages                                             |       |

| iSBC 635 Power Supply                                              |       |

| iSBC 640 Power Supply                                              |       |

| iSBC 655 System Chassis                                            |       |

| iSBC 660 System Chassis                                            |       |

| iSBC 661 System Chassis                                            |       |

| iSBC 665 System Chassis                                            |       |

| iSBX I/O Expansion Bus                                             |       |

| iSBX 217C 1/4-inch Tape Drive Interface MULTIMODULE Board          |       |

| iSBX 218A Flexible Disk Controller                                 |       |

| iSBX 251 and 251C Bubble Memory                                    |       |

| iSBX 258 Interface MULTIMODULE for Intel Bubble Cassette System    |       |

| iSBX 270 Alpha-Numeric Display Controller                          |       |

| iSBX 275 Video Graphics Controller                                 |       |

| iSBX 311 Analog Input MULTIMODULE Board                            |       |

| iSBX 328 Analog Output MULTIMODULE Expansion Board                 |       |

| iSBX 331 Fixed/Floating Point Math MULTIMODULE Board               |       |

| iSBX 337/337A MULTIMODULE Numeric Data Processor                   |       |

| iSBX 344 BITBUS Remote Controller MULTIMODULE Board                |       |

| iSBX 350 Parallel I/O MULTIMODULE Board                            | 11-16 |

# Alphanumeric Index

| iSBX 351 Serial I/O MULTIMODULE Board                | 11-20 |

|------------------------------------------------------|-------|

| iSBX 352 Bit Serial Communications MULTIMODULE Board | 11-26 |

| iSBX 354 Dual Channel Serial I/O MULTIMODULE Board   | 11-32 |

| iSBX 488 GPIB MULTIMODULE Board                      | 11-37 |

| iSDM 86 System Debug Monitor                         | 6-37  |

| iSDM 286 iAPX 286 System Debug Monitor               | 4-50  |

| iSYP 384 System Chassis                              | 12-25 |

| iVDI 720 Virtual Device Interpreter                  | 9-19  |

| iXSM Series Extention Modules                        |       |

| MULTIBUS System Bus                                  | . 3-1 |

| MULTIBUS II iLBX II Local Bus Expansion              | . 4-1 |

| MULTIBUS II iPSB Parallel System Bus                 | . 4-7 |

| MULTIBUS iSSB Serial System Bus                      | 4-20  |

| MULTICHANNEL I/O Bus                                 | 3-11  |

| Third Party Software for Intel Systems               | 1-30  |

| System 310 Microcomputer System                      | 1-19  |

| System 310 Reliability                               | 1-51  |

| System 380 Microcomputer Systems                     | 1-24  |

| XENIX Languages                                      | 1-33  |

| XENIX 3.0 Operating System                           | 1-37  |

| 310 MS-DOS (2.11) Operating System                   | 1-43  |

| 311 Peripheral Expansion Sub-System                  | 1-47  |

|                                                      |       |

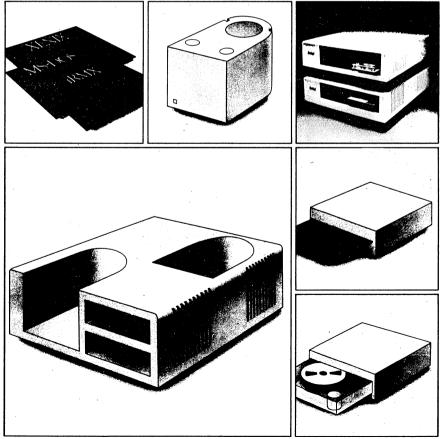

### ISXM™ SERIES SYSTEM EXTENSION MODULES

- iSXM<sup>™</sup> 101 Memory Management and Protection Extension Module for XENIX¹-86 multi-user microcomputer systems

- iSXM<sup>™</sup> 534 Four-channel Serial Communication Extension Module for multi-user systems

- iSMX<sup>™</sup> 544 and iSXM<sup>™</sup> 544A Intelligent Four-channel Serial Communication Extension Modules for high-performance multi-user systems

- iSXM<sup>™</sup> 951 RS232 Serial I/O Cable Extension Module for use with iSXM 534 or 544 in Intel SYSTEM 310 Family microcomputer systems

- iSXM<sup>™</sup> 953 RS232 Serial I/O Cable Extension Module for use with iSXM<sup>™</sup> 534 or 544 in Intel SYSTEM 380 Family microcomputer systems, or as a second cable set for the SYSTEM 86/330A

- iSXM<sup>TM</sup> 955 Communication Cabling for use with the iSBC<sup>®</sup> 188/48 Eight Channel Communication board in the SYSTEM 310 Family

- iSXM<sup>TM</sup> 956 Communication Cabling for use with the iSBC® 188/48 Eight Channel communication board in the SYSTEM 380 Family

The iSXM™ family of System Extension Modules is designed to extend the hardware capability of the SYSTEM 86/300 and SYSTEM 286/300 Series microcomputers. All hardware is fully configured and can easily be installed in the system. An easy-to-follow installation manual as well as all hardware documentation is included in each package.

<sup>†</sup> XENIX is a trademark of Microsoft Corporation

The following are trademarks of Intel Corporation and may be used only to describe Intel products: Intel, ICE, iMMX, IRMX, ISBC, ISBX, ISXM, MULTIBUS, Multichannel and MULTIMODULE. Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supercedes previously published specifications on these devices from Intel.

<sup>©</sup> INTEL CORPORATION, 1983

# iSXM<sup>™</sup> 101 XENIX<sup>†</sup> Memory Management and Protection Module

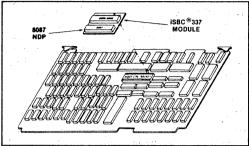

This module contains the iSBC® 309 Memory Management and Protection MULTIMODULE™ board, the iAPX 8087 Numeric Data Processor Device, all associated mounting hardware and an installation guide for use in the SYSTEM 86/300 Series microcomputers.

XENIX<sup>1</sup>-86 takes advantage of these hardware features through the use of a dynamic scatter loading technique. This memory management method allows programs to be loaded in non-contiguous blocks of RAM for more efficient memory utilization.

XENIX-86 Release 2.0 supports the 8087, giving the host processor greatly enhanced math execution capability.

The two-level diagnostic program featured in Intel SYSTEM 86/300 Series microcomputers supports the iSXM™ 101.

For more details, please refer to the iSBC 309 and iAPX 8087 data sheets.

# ISXM™ 534 Four-Channel I/O Extension Module, ISXM™ 544 and ISXM™ 544A Intelligent Four-Channel I/O Extension Module

The iSXM 534 contains the iSBC 534 Four-channel Serial Communications Board, fully configured for use in Intel SYSTEM 300 Series microcomputer systems, installation instructions and a Hardware Reference Manual.

The iSXM 544 Intelligent Four-Channel Serial I/O Module contains the iSBC 544 board, fully configured for use in Intel SYSTEM 300 Series microcomputer systems, two 2732A EPROMS containing firmware to control the iSBC 544, installation instructions and Hardware Reference Manual.

installation of these modules adds four serial I/O channels to the one already resident on the 86/30 processor board, or to the two resident on the 286/10 processor board. They interface directly to the system through the MULTIBUS® system bus. The four serial ports fully support RS232C (configured) asynchronous communications.

The iSXM 544 provides much higher I/O performance, making it particularly suited for multiuser requirements.

The iSXM 554A is functionally equivalent to the iSXM 544 and offers 16 MB addressability.

These System Extension Modules are fully supported by iRMX™ 86 Release 5, XENIX 86 Release 2 and XENIX 286.

Cables and mounting hardware are required for use in Intel microcomputer systems. Order the iSXM 951, 952, or 953 depending on your system type.

For a full explanation of the iSBC 534 or iSBC 544, please refer to the respective data sheets.

#### iSXM™ 951 RS232 Serial I/O Cables

This module contains four 1-foot cables for use from the edge connectors of the iSXM 534 or 544 to the back of the SYSTEM 86/310 Series or SYSTEM 286/310 Series chassis. An installation guide is also included.

#### ISXM™ 953 RS232 Serial I/O Cables

173077-001 iSXM 101 Installation Guide

This module contains four 2-foot cables for use from the edge connectors of the iSXM 534 or 544 to the back of the SYSTEM 86/380 Series or SYSTEM 286/380 Series chassis, and an installation guide.

#### **Reference Manuals**

| 144686     | iSBC 309 Hardware Reference Manual                  |

|------------|-----------------------------------------------------|

| 173177-001 | System Terminal Communication<br>Installation Guide |

| 980450     | iSBC 534 Hardware Reference Manual                  |

| 980616     | iSBC 544 Hardware Reference Manual                  |

| 173074-001 | iSXM 951 Installation Guide                         |

| 173076-001 | iSXM 953 Installation Guide                         |

|            |                                                     |

#### **Ordering Information**

| •                    |                                               |

|----------------------|-----------------------------------------------|

| iSXM 101 or PSXM 101 | Memory Management<br>Module                   |

| iSXM 534 or PSXM 534 | 4-channel I/O Extension Module                |

| iSXM 544 or PSXM 544 | Intelligent 4-channel I/O<br>Extension Module |

ISXM 544A or PSXM 544A 16 MB Intelligent 4 Channel I/O Extension Module

| ISXM 951 or PSXM 951 | Cables for SYSTEM 86/310,<br>SYSTEM 286/310 |  |

|----------------------|---------------------------------------------|--|

| iSXM 953 or PSXM 953 | Cables for SYSTEM 86/380,                   |  |

SYSTEM 286/380

iSXM 955 or <sup>P</sup>SXM 955 Cables for the iSBC 188/48

in any SYSTEM 310

iSXM 956 or PSXM 956 Cables for the iSBC 188/48 in any SYSTEM 380

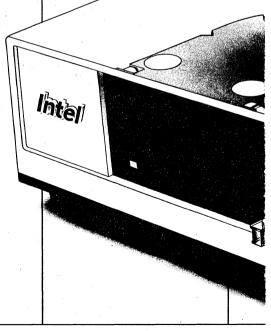

### Database Information System iDIS™ 715

- Building block for departmental-level applications

- Data Pipeline™ system to distribute databases

- Direct mainframe database extract and file transfer facilities

- Gateway for personal computer and terminal access

- Multiuser XENIX\* 3.0 operating system

- · Local relational database management and report writer

- Integrated software with on-line help facility

- Word processing, spreadsheet, graphics, menu development, and communication options

- C programming language

- Desk-top integrated microsystem

- Worldwide vendor service and support

- \*XENIX is a registered trademark of Microsoft Corporation.

1984 Intel Corporation

September 1984 ORDER NUMBER 210712-005

#### Building Vertical Applications with the iDIS™ System

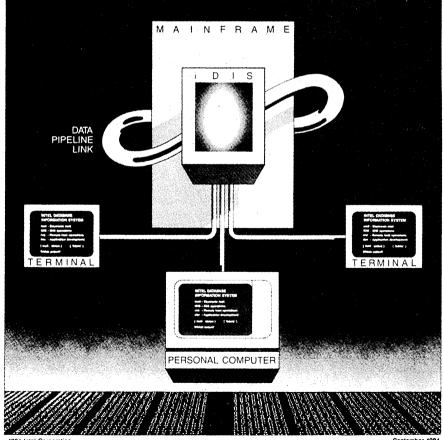

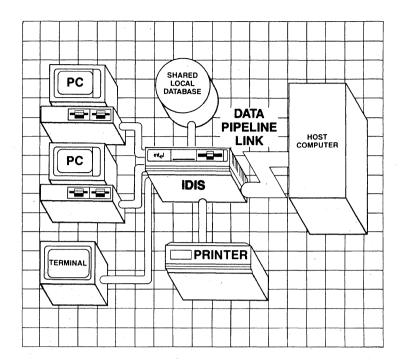

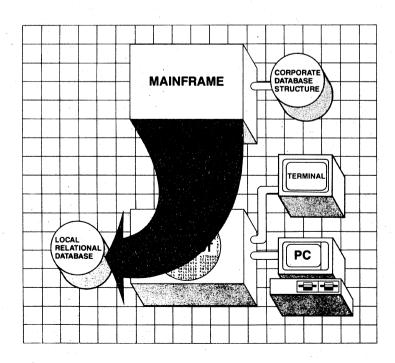

The Intel Database Information System (iDIS™) is a fully-integrated multiuser hardware/software microcomputer system. It serves as a building block for end-user applications and a powerful access tool in the Data Pipeline connection between a mainframe and the end-user. Data can be maintained by central data processing departments and distributed to departmental users through a network of terminals and PCs. The system can be configured as a gateway in the microto-mainframe flow of data or as a stand-alone processor with shared local database capabilities. The iDIS system includes an SQL-compatible, multiuser relational DBMS for shared access to disk storage and features a full range of information processing functions for multiple concurrent users at all levels of technical skill

### The iXTRACT remote database extract facilities

The iDIS system offers two interactive, menu-driven modes of database extract. With the Remote File Transfer (RFT) iXTRACT facility, a "flat file" (sequential) data structure can be downloaded from the mainframe and converted into a local relational database. Using host computer utilities to generate the flat file, the RFT facility can download data from virtually any DBMS or file management system. The facility is bidirectional, such that flat files can be transmitted between a mainframe host and an iDIS system with its network of terminals and personal computers.

A second facility, the Direct iXTRACT facility, is a menu-driven data extract facility which directly downloads Intel SYSTEM 2000® databases (from IBM, CDC, and Sperry environments) into an iDIS database. Both RFT and direct modes allow non-technical users to access remote corporate databases and extract information while central data processing controls data security at every terminal.

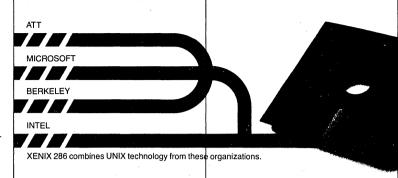

#### Microsoft XENIX

The iDIS operating system is provided by XENIX 3.0, an enhanced industry-standard version of UNIX\* XENIX is a general-purpose, multiuser, interactive operating system designed to make the computing environment simple, efficient and productive for a wide range of users. While the system developer has access to all XENIX functionality, the operating system appears to be transparent to the user who interacts with the iDIS software through its menu system.

The XENIX system supplies:

- A flexible and logical hierarchical file system, with cross-directory file linking and multiple protection and security modes

- The XENIX shell command language, with conditional, recursive, and iterative constructs (for development of user/application procedures)

- Sequential, asynchronous, and background process execution

- Sophisticated editing and textprocessing facilities supporting printers and typesetters

- Device-independent input and output.

## The iDB-local relational database management (DBMS)

The iDIS system offers the iDB DBMS, a full-function relational DBMS that supports an interactive query/update language similar to that of IBM's SQL. Included with iDB is a Report Writer package. This allows users to prepare custom reports quickly from information in iDB without programming knowledge. The iDB DBMS offers all the power of a mainframe DBMS at the microsystem level. Multiple iDB users can concurrently access common local databases with confidence in system integrity.

Other features include:

- A user-prompting data entry and update subsystem

- A bulk loading and unloading utility for rapid transfer of data among files and databases

- Extensive on-line help facilities

- Descriptive error and diagnostic messages

- Programmatic interface to the C language and XENIX shell.

#### Seamless™ software interface

The iDIS software family is integrated into a Seamless set of productivity tools. Data can be easily transferred among the various iDIS application packages, such that the iWORD processor, iPLAN (Multiplan\*) spreadsheet, and iDB DBMS can interchange data and reports. All iDIS decision-support tools can be easily brought to bear on a particular data-analysis problem.

Individually, each package is accessible through a common user interface—a hierarchical menu system serving as a superstructure for the complete iDIS system. A common help facility binds all iDIS software.

#### The iWORD processor

The Intel iWORD facility is a sophisticated word processing tool that supports a complete office-wide range of document preparation functions. The iWORD user can develop, edit, store, format and print a variety of presentation-quality business documents, including reports, memoranda, technical documents, specifications and manuals. All iWORD commands are in plain English and many can be executed by a single keystroke. The iWORD processor is also sufficiently powerful for the experienced user, offering access to XENIX text processing capabilities including the printerand typesetter-drivers nroff and troff. An on-line help facility is continuously available.

Major iWORD editing and formatting features include:

- Full-screen editor with on-line display of formatted text

- Embedded commands for global formatting

- Spelling/dictionary module and mail/merge facility

- Right justification, underlining, indentation, centering, footnotes, superscripts and subscripts.

<sup>\*</sup>UNIX is a trademark of AT&T Bell Laboratories. Multiplan is a registered trademark of Microsoft Corporation.

## The iPLAN (Multiplan) spreadsheet

The iDIS system supports 'what if' decision-modeling with iPLAN (Multiplan) Spreadsheet, a multipurpose tool capable of a wide variety of business and scientific tabulations. The iPLAN user can custom-tailor a versatile two-dimensional matrix for specific analyses, including financial modeling, planning and forecasting. Like the other functions in the iDIS software environment, the iPLAN spreadsheet accepts data four ways: from the keyboard, from the iDB DBMS, from mainframe databases (via the data extract facility), and from formatted XENIX files.

Important iPLAN features include:

- Easy-to-use English commands

- Vertical and horizontal scrolling, multi-window and multi-table display

- Presentation of extra large tables

- Linking and updating multiple interrelated spreadsheets

- Automatic updating of calculations

- Alphanumeric sorting capabilities

- Extensive, on-line help facility.

### The personal computer (iPC) connection

To complete the Data Pipeline connection, the iDIS system offers a menu-driven file conversion and transfer facility that allows single-user PC files to be accessed in the multiuser XENIX environment. The PC user can use the iDIS system to convert database and spreadsheet files from popular PC file formats (such as dBASE II\* Lotus 1-2-3\* and Multiplan formats) to iDB file formats. As a result, mainframe files can be downloaded to relational structures within iDB databases and further converted and downloaded to PC-based files for local applications analysis. The PC user can operate in three modes: bidirectional iDIS-to-PC file transfers, iDIS terminal emulation, and local PC-DOS control.

#### Office automation features

The XENIX operating system provides an electronic mail service in which business messages are shared and relayed with ease. XENIX also includes handy "desk calculator" functions and an electronic calendar that provides an automatic reminder (via electronic mail) of any user appointments.

### Application development tools

The iDIS application development subsystem includes such software tools as the iMENU development system, C programming language, the XENIX Shell program, and the full-screen 'vi' editor (visual editor). These tools support efficient development and maintenance of program and text files by technical users.

The iDIS system offers a complete program development and execution environment for C, the versatile general-purpose language in which the operating system and all iDIS application packages are implemented. C maximizes development productivity by its structured programming methodologies and standard flow-control constructions—if, while, for, do, and switch (case). It provides pointers, the ability to perform address arithmetic, and recursive functions. Many existing C-based applications can be efficiently ported to the iDIS system.

# The iMENU development facility

The iMENU development facility provides the iDIS system-level user interface, tying together the XENIX operating system, iDIS applications software, and help system. The iMENU facility retains and yet simplifies full XENIX functionality. Programmers and non-programmers alike can use the iMENU facility in creating or modifying menus, forms, and help screens for existing or custom-developed applications.

#### The on-line help facility

The help facility, a comprehensive on-line documentation feature, is integrated with the menu system so the user need not refer to hard copy reference manuals when using iDIS applications. Experienced users can employ the iMENU facility to extend or modify the help facility to specify help procedures for custom applications.

#### The iGRAPH facility

The iDIS system offers a presentation graphics package, iGRAPH, that provides high quality output to most

\*dBASE II is a trademark of Ashton-Tate. tronic mail Lotus and 1-2-3 are trademarks of Lotus Development Corporation.

standard graphics peripherals. Through iDIS integration, data can easily be moved from iPLAN and iDB to iGRAPH, from iGRAPH to iWORD for printed output, and to and from iPC. Graphic peripherals supported are Tektronix 4105, color terminal, Televideo 950 monochrome terminal with Retrographics board, Hewlett-Packard HP7475 plotter, the Epson MX80 printer, and the IBM PC with graphics board. The Intel terminal can be used to generate graphics hard copy.

#### Communications

The iDIS communications subsystem provides remote job entry (RJE) to mainframe hosts through its emulation of a HASP multileaving workstation or 2780/3780 protocol. TTY passthrough facilities also provide direct access to remote interactive applications. including other iDIS systems and personal computers. Support for 3270 BCS emulation is also available, and SNA support is planned.

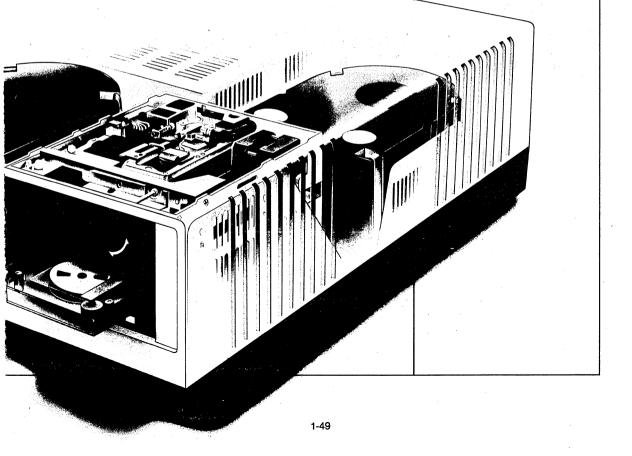

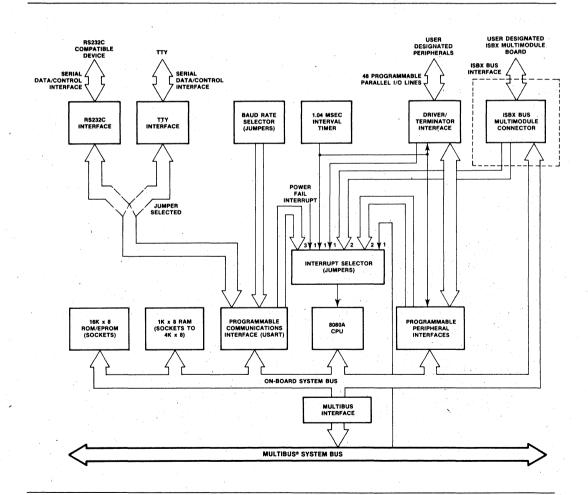

### BASE SYSTEM HARDWARE Processor

The iDIS 715 uses the MULTIBUS®-based iSBC® 286/10 board with the 80286 processor. An Intel 80287 co-processor is standard to provide significant performance boost for numeric operations. Instructions are 8, 16, or 32 bits in length; data are 8 or 16 bits long; numeric processing, with the 80287, is carried out in 80-bit words. Memory management and protection are also included.

One megabyte of high-performance RAM with ECC is standard. To provide faster access, Intel memory boards are connected directly to the 286/10 processor board via iLBX™ (Local Bus Exchange).

#### **Communications support**

Asynchronous communication and synchronous mainframe communications support is handled by an iSBC 188/48 Advanced Communications Processor Board. Eight connections can be configured for terminals, PCs and/or mainframe communications.

#### **MASS STORAGE**

Winchester disk drive—The iDIS 715 contains a 40 MB 514" Winchester technology disk drive for program and data storage. The drive has an average access time about 40 milliseconds and a transfer rate of 6.44 Mbits/sec.

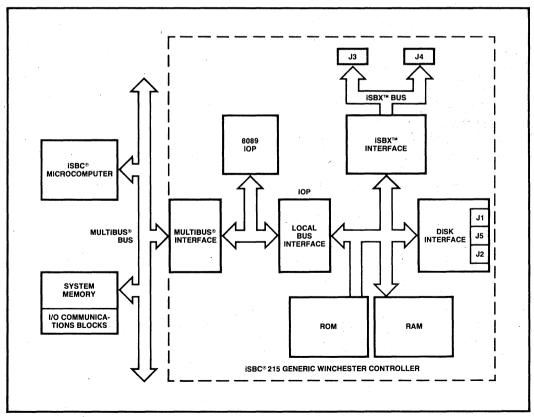

Intelligent controller—The iDIS 715 includes an intelligent, 8089-based iSBC 215 Winchester controller. This high performance interface contains firmware which is executed directly on the iSBC 215 controller to offload a significant portion of disk I/O overhead from the host 80286 processor. In addition, the iSBC 215 board supports an iSBX<sup>IM</sup> 218 controller to manage the floppy disk.

Floppy disk drive—A 5¼" 320 KB floppy disk drive is included in the base system. This floppy drive has an average access time of 91 milliseconds and a transfer rate of 250 KB/sec.

#### Optional peripherals

**Display terminal**—The standard iDIS system can connect up to 10 terminals. The terminal connected to the

console port can be used for system control and administration, as well as a regular workstation. An iDIS terminal is also available, with 24-80 character lines and a 25th status line. The 96 upper and lower ASCII characters are formed in a 7x9 matrix in an 8xI0 cell. The screen is non-reflective and uses green P3I phosphor.

Printer—The iDIS system supports a Centronics-compatible printer. A dot matrix character printer capable of 200 character-per-second bidirectional printing is also available. It includes a Centronics-compatible parallel interface and a 218-character buffer. The printer features a 7×9 dot matrix to form all 96 ASCII characters. Maximum standard print line length is 132 characters or 218 with condensed print. The Intel printer prints 10 characters per inch; spacing of 5, 8.25, and 16.5 characters per inch can also be accommodated.

#### System support

The iDIS system is fully supported by Intel's worldwide service staff, including a group of information system

professionals with over 15 years experience in commercial database technologies. Support for iDIS applications software is included with the system price for 90 days and is optional thereafter. All iDIS software with a current software maintenance agreement is supported by the Intel Austin Systems Support Hotline.

In addition to the hotline, system support includes software updates, customer problem reporting, and a product newsletter. Intel provides comprehensive training classes on all iDIS applications, the XENIX operating system, programming languages, and hardware operation.

The iDIS hardware includes a warranty for 90 days mechanical, 45 days labor, and 90 days electrical components. After the warranty period, subscription maintenance is available from the Intel field service organization. Hardware service is also available for users on a per-call basis.

### Extensive system documentation

The iDIS 715 is shipped with multiple hardware and software manuals that address all aspects of system operations. Software documentation includes manuals on the XENIX Release 3.0 operating system, iDB and Report Writer software, and each optional application package that is ordered. General overviews and detailed tutorials are an integral part of this documentation. A system installation and maintenance manual, a system overview manual, and a site preparation manual are also provided.

iWORD is a version of Horizon Word Processing, a trademark of Horizon Software Systems, Inc. iPLAN is a version of Microsoft's Multiplan, a trademark of Microsoft Corporation. iMENU is a version of Schmidt's /menus, a trademark of Schmidt Associates.

Information contained herein supersedes previously published specifications on these devices from Intel.

### SYSTEM CONFIGURATION Base Hardware System:

- 1 MB of RAM memory

- 320 KB floppy drive

- 40 MB Winchester disk

- Support for up to 10 terminals and/or PCs

- Printer support for Centronicscompatible printer

- · Disk controller board

- · Communications processor

#### **Optional Hardware:**

- Additional communications processor

- · Terminals and dot-matrix printers

#### **Base Software System:**

- XENIX 3.0 operating system

- C programming language

- 'vi' editor

- XENIX utilities (including nroff and troff text processors)

- · Electronic mail and calendar

- · iDB and Report Writer

- iMENU (runtime) system

- · Help facility

- · Complete systems diagnostics

#### **Optional Software:**

- iWORD word processor

- iPLAN (Multiplan) spreadsheet

- iMENU menu development system

- · Direct iXTRACT facility

- Remote File Transfer facility

- iPC (personal computer link)

- · iGRAPH presentation graphics

- RJE communication support (2780/3780 and/or HASP protocol)

- 3270 BSC emulation

### SPECIFICATIONS Instruction cycle time

250 nanoseconds for fastest executable instructions.

#### Disk

Standard 40 MB Winchester disk; Second 40 MB disk is planned.

#### External/PC interface

Serial – 8 asynchronous ports, configurable from 110 to 9600 baud. EIA Standard RS232C signal support is provided.

Parallel – one Centronics-compatible parallel I/O port for printer connections.

### Regulatory Agency Specifications

Meets ULII4-Safety; CSA 22.2-Safety; FCC Docket 20780-RFI/EMI. Designed to meet IEC 435-Safety; VDE 087I-RFI/EMI.

# ENVIRONMENTAL OPERATING REQUIREMENTS

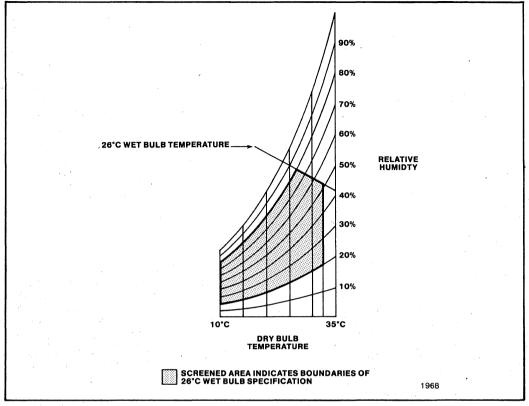

Altitude—Sea level to 8000 feet. Temperature—15 degrees C to 35 degrees C.

Relative humidity – 20% to 80% non-condensing over the operating temperature range. The environmental combination of humidity and temperature together cannot exceed 26 degrees C wet bulb.

The Intel Database Information System (iDIS 715) is a multiuser XENIX 286-based microcomputer system that includes a complete set of end-user productivity and application development tools. The iDIS system can be purchased as an integrated hardware/software microcomputer system configured for specific departmental computing applications. In addition, the various iDIS productivity tools, application development tools, relational database management system, and communication software options can be purchased separately to run on XENIX-based Intel microcomputers.

### iRMX™ LANGUAGE

- Industry-standard languages and utilities for developing applications on iRMX-based systems. Includes FORTRAN, Pascal, C, BASIC, PL/M, assembler, text editor

- Complete set of utilities to create and manage object modules

- Mix languages on single application system with UDI standard

- Intel 8087 and 80287 math coprocessor support

- 8086 and 80286 compatibility

- Worldwide post-sales service and support organization

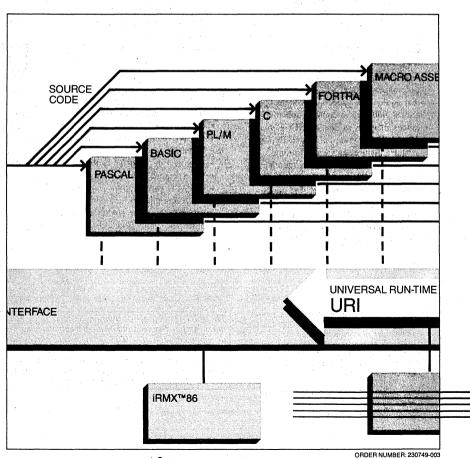

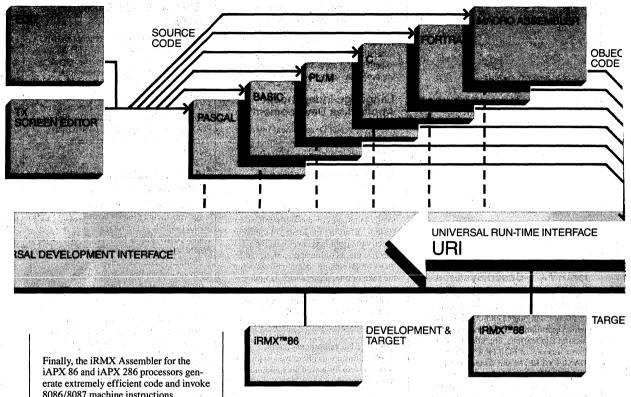

### Full Language Support for iRMX™ -Based Systems

Intel's iRMX™ 86 based systems are completely supported by a wide variety of popular languages and utilities with which to build fast, real-time, multitasking applications. Included are the latest versions of FORTRAN, Pascal, BASIC, C, PL/M and Assembler for Intel's iAPX 86 and iAPX 286 processors. Previously developed applications using any of these languages port easily to iRMX-based systems with minimal source code modifications.

In addition to the wealth of languages available, iRMX-based systems are complemented by utilities with which to create and manage object modules. This latitude in configurability allows programmers to team their efforts in order to achieve a shorter development time than would otherwise be possible.

Because the high-level languages are actually resident on the iRMX-based system, OEMs can pass application software directly on to end users. End users may then tailor the OEM's system to better meet application needs by writing programs using the same languages.

#### Language-Independent Application Development

Intel's Universal Development Interface (UDI) and Object Module Format (OMF) enable several users to write different modules of an application, in different languages, then link them together.

The OMF provides users with the ability to mix languages on a single application system, affording the luxury of choosing exactly the right language tools for specific pieces of the application, rather than compromising specialized tasks for the sake of one, project-wide language.

iRMX languages are fully compatible with the Intel Series III and Series IV Development Systems, should the user choose to develop applications on a specialized development system. Applications are easily moved to the final target system for test, debug and minor redevelopment.

### Fast, Lean Programs for Rapid Processing

The iRMX language products enable programmers to write the smallest, fastest programs available in high-level languages, due to the compiler's superior ability to optimize code.

It is also possible to make iRMX operating system calls directly from FORTRAN, PASCAL and PL/M. This means that application developers can take full advantage of the iRMX multitasking capability, whereby multiple applications execute concurrently on the operating system. Multitasking, a requirement of most real-time systems, is sometimes as necessary in application software development as in an operating system environment.

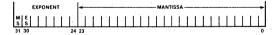

### Standardized REALMATH Support

All the iRMX languages (except BASIC and C) support the REALMATH floating point standard. This ensures universal consistency in numeric computation results and enables the user to take advantage of the Intel iAPX 86/20 and iAPX 88/20 Numeric Data Processor or iSBC<sup>®</sup> 337 MULTIMODULE™ boards, which boost performance two to four times over that possible on a minicomputer.

### All the Utilities Needed to Link Languages

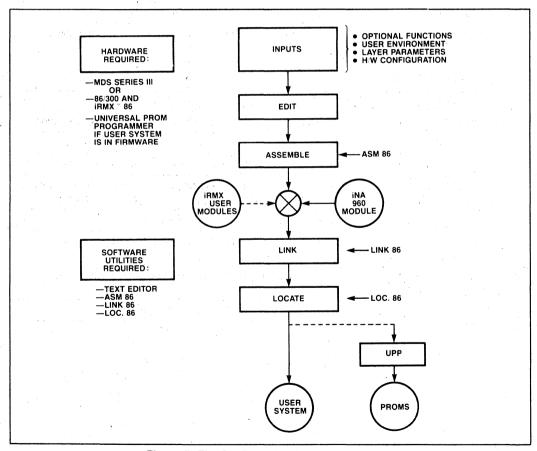

Utilities for iRMX operating systems include Intel's own EDIT, LINK, LOCATE and LIBRARIAN. The iRMX EDIT program meets the needs of both novice and sophisticated users with powerful line-oriented editing facilities.

Using the iRMX LINK program, users may link individually compiled object modules to form a single, relocatable object module. This provides the ability to merge work from several programmers into one cohesive application system.

The iRMX LOCATE utility maps relocatable object code into the processor memory segments, allowing user definition of module/memory type allocation. For example, often-used portions of an application may be mapped to (P)ROM.

The LIBRARIAN object code library manager affords easy creation, collection and maintenance of related object code to reduce the overhead of separately maintained modules.

8086/8087 machine instructions.

#### iRMX™ 86 Pascal

iRMX Pascal meets the proposed ISO language standard and implements several microcomputer extensions. A compile-time option checks conformance to the standard, making it easy to write uniform code. Industry-standard specifications contribute to portability of application programs and provide greater reliability.

iRMX 86 Pascal supports extensions, such as an interrupt-handler and direct port I/O extension, that allow programs to be written specifically for microcomputers. Separate module compilation allows linkage of Pascal modules with modules written in other high-level languages.

For more information on iRMX 86 Pascal see the Pascal 86 Software Package data sheet.

#### **IRMX™ 86 FORTRAN**

The iRMX 86 FORTRAN compiler provides total compatibility with FORTRAN 66 language standards, plus most new features provided by the FORTRAN 77 language standard, iRMX 86 FORTRAN includes extensions specifically for microcomputer application development. Programming is simplified by relocatable object libraries, which provide run-time support for execution time activities.

iRMX 86 FORTRAN supports the 8087 math coprocessor for the most powerful

microcomputer solution available in number-intensive applications. For more information on iRMX 86 FORTRAN see the FORTRAN 86 Software Package data sheet.

#### IRMX™ 86 PL/M

PL/M offers full access to micro-computer architecture while simultaneously offering all the benefits of a high-level language. Invented by Intel in 1976, PL/M 80 was the first microcomputer-specific, block-structured, high-level language available. Since then, thousands of users have generated code for millions of microcomputer-based systems using PL/M 80 and PL/M 86.

Software written for 8-bit processors (PL/M 80) are easily ported to the more powerful 16-bit (PL/M 86) environment. The same portability will be available for future VLSI.

For more information about iRMX 86 PL/M see the PL/M 86/88 Software Package data sheet.

#### **IRMX™ 86 BASIC**

Intel's offering of Microsoft BASIC is a standardized version of the most popular high-level language in the world. Existing BASIC programs are easily ported to iRMX-based systems. BASIC is an excellent pass-through language by which an OEM can offer customers the ability to write and modify their own applications.

#### iRMX™ 86 C Compiler

The popular new programming language, C (Mark William's Company version), is fully supported on iRMX-based systems. iRMX 86 C offers both small and large

segmentation models, enabling applications to be written efficiently. The iRMX 86 C compiler combines assembly language efficiency with high-level language convenience; it can manipulate on a machine-address level while maintaining the power and speed of a structured language.

The iRMX 86 C compiler affords easy portability of existing C programs to iRMX-based systems. For more information on the iRMX C compiler see the iRMX 86 C Software Package data sheet.

#### iRMX™ 86 Text Editor

The iRMX 86 Text Editor is screenoriented, menu-driven and easy to learn. Guided by the menu of commands always before him, the user can edit text and programs easily and efficiently.

iRMX 86 Text Editor allows the simultaneous edit of two files. This allows easy transferral of text between files and use of existing material in the creation of new files. Creating macros, strings of frequently-used commands, is also very simple. The editor "remembers" the selected commands and allows the user to re-use them repeatedly.

### Worldwide Service and Support

All iRMX systems are completely supported by Intel's worldwide staff of trained hardware and software engineers. iRMX Language customers receive a warranty that includes Hotline Support, Software Updates, and Subscription

Complete documentation is provided for all operating system and application software languages, as well as for system hardware components. An Intel system is not a collection of hardware and software pieces as much as a cohesive whole that is supported and serviced as such.

### Intel Has Total Solutions for Real-Time Systems

iRMX 86 is the fastest, most powerful operating system available for multitasking, multi-user, real-time applications. Complemented by a wide range of industry-standard languages and utilities, the iRMX-based systems are highly flexible and configurable.

Application development for iRMX-based systems is possible at the board or the system level. OEMs can integrate functionality at the most profitable level of product design, using one system for both development and target use. Intel's choice of industry standard high-level languages enables the end user to extend OEM-provided functionality even further, if desired.

Who is better qualified to write and supply software for Intel VLSI than Intel? Today you have the ability to tap into hundreds of available application software packages, languages and utilities, peripherals and controllers and MULTIBUS® boards.

Tomorrow, and ten years down the road, you will be able to tap into the latest, high-performance VLSI—without losing today's software investment.

#### **Specifications**

#### Required Hardware

- Any iAPX 86/286 based or iSBC 86/286 based system including Intel's System 86/300 and 286/300 family. In addition, object code from the compilers will run on iAPX 88 based systems.

- 140KB of memory

- Two iRMX 86 compatible floppy disks or one hard disk

- One 8" double density or 5.25" doubledensity floppy disk drive for distribution of software

- System console device

#### Required Software

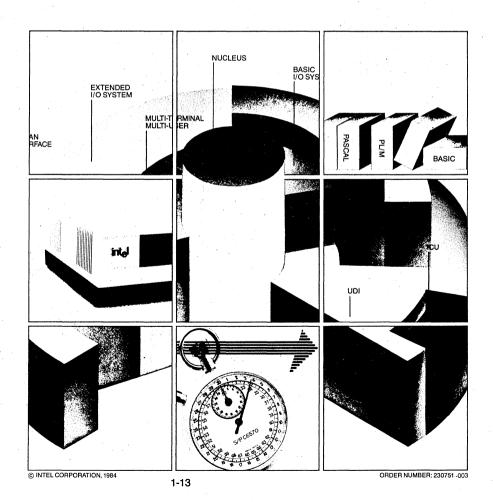

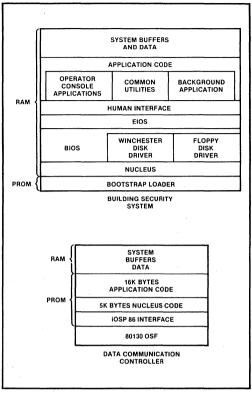

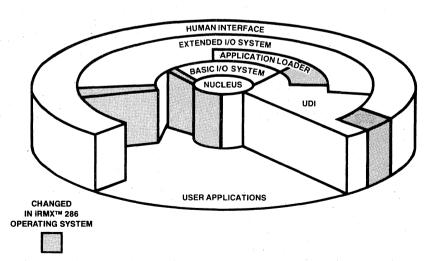

The iRMX 86 Operating System Release 6 or later including the nucleus, basic I/O system, extended I/O system and human interface

Purchase of any RMX language requires signing of Intel's OEM License Agreement (OLA).

#### **Ordering Information**

|                      |            |                                                                                                                                                                                                                  | State of the second                                                    |

|----------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Language             | Order Code | Product Contents                                                                                                                                                                                                 | Warranty                                                               |

| ASM 86,<br>Utilities | RMX 860    | Two 8" disk and two 5.25" diskettes Edit Reference Manual iAPX 86/88 Family Utilities User's Guide Macro Assembler Operating Instructions ASM 86 Language Reference Manual 8087 Support Library Reference Manual | 90 days:<br>Software Updates, Subscription Service,<br>Hotline Support |

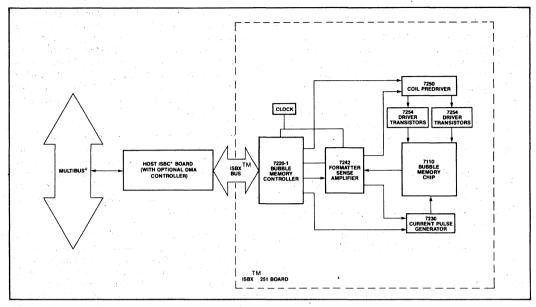

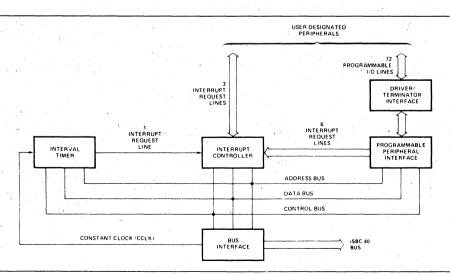

| Pascal               | RMX 861    | Two 8" diskettes and two 5.25" diskettes<br>Pascal 86 User's Guide                                                                                                                                               | 90 days:<br>Software Updates, Subscription Service,<br>Hotline Support |